## ЦИФРОВОЙ ФАЗОВЫЙ ДЕТЕКТОР

## ОСНОВНЫЕ ХАРАКТЕРИСТИКИ

Микросхема предназначена для измерения фазового рассогласования между импульсными последовательностями генератора опорной частоты и генератора, управляемого напряжением, а также формирования импульсных последовательностей с заданными параметрами.

Микросхема может быть использована для решения следующих задач:

- частотная модуляция и демодуляция;

- синтез, измерение и умножение частоты;

- преобразование типа «напряжение – частота»;

- синхронизация потоков данных;

- управление скоростью вращения двигателей.

|                                                                 |                |

|-----------------------------------------------------------------|----------------|

| Максимальная частота сравниваемых последовательностей, МГц..... | 45             |

| Разрядность кодов управления делителями частоты, бит.....       | 9              |

| Напряжение питания, В.....                                      | +5 ± 10%       |

| Температурный диапазон, °С.....                                 | от -60 до +125 |

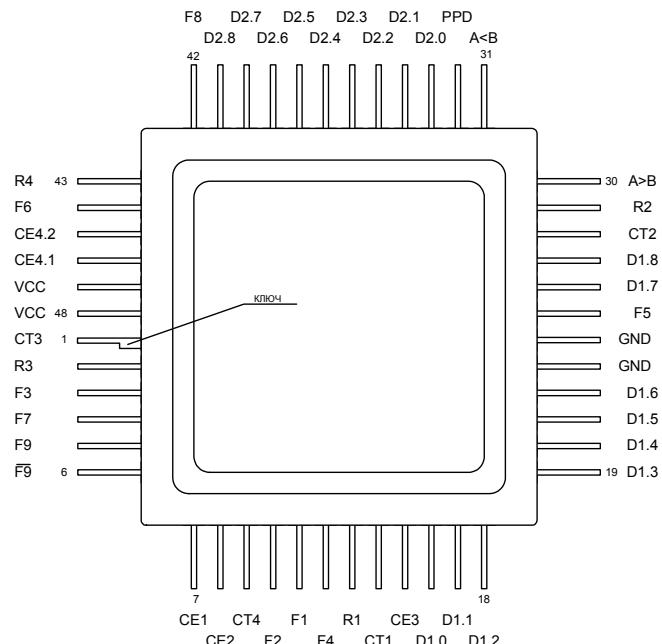

| Тип корпуса.....                                                | H16.48-1В      |

Микросхема изготавливается по КМОП технологии и имеет ТТЛ-совместимые входы и выходы.

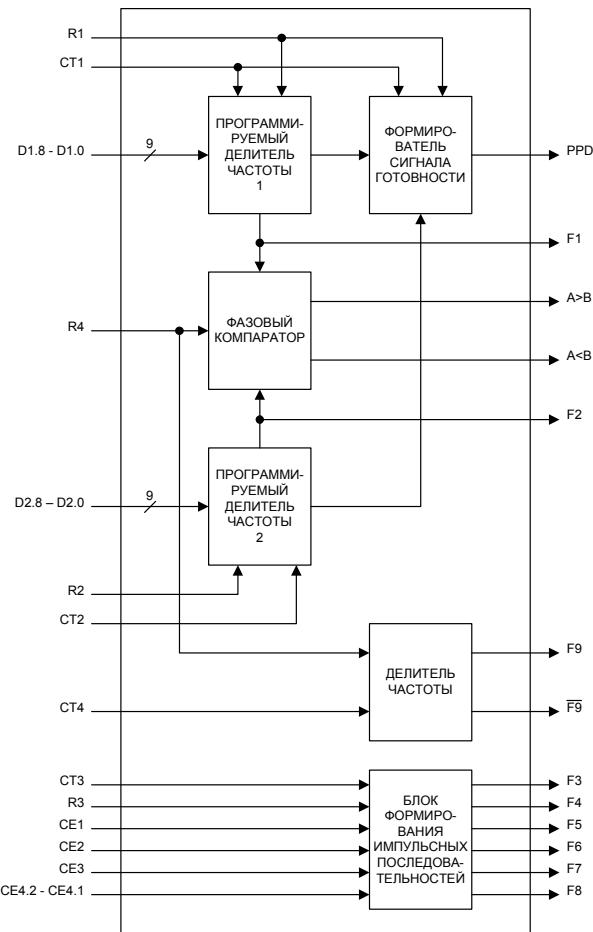

## **СТРУКТУРНАЯ СХЕМА**

## НАЗНАЧЕНИЕ ВЫВОДОВ

| Обозначение | Назначение                                                       |

|-------------|------------------------------------------------------------------|

| D1          | Входная шина кода коэффициента деления первого делителя частоты  |

| D2          | Входная шина кода коэффициента деления второго делителя частоты  |

| СТ1         | Вход синхронизации                                               |

| СТ2         | Вход синхронизации                                               |

| R1          | Вход разрешения предустановки первого делителя частоты           |

| R2          | Вход разрешения предустановки второго делителя частоты           |

| F1          | Выход первого делителя фазового детектора                        |

| F2          | Выход второго делителя фазового детектора                        |

| A>B         | Выход сигнала сравнения фазового детектора                       |

| A<B         | Выход сигнала сравнения фазового детектора                       |

| PPD         | Выход готовности фазового детектора                              |

| СТ3         | Вход синхросигнала                                               |

| СТ4         | Вход синхросигнала.                                              |

| СЕ1         | Вход управления последовательностями 5315/5335                   |

| СЕ2         | Вход управления последовательностями 5335/5315                   |

| СЕ3         | Вход разрешения выдачи последовательности 15/1                   |

| СЕ4         | Входная шина кода управления последовательностями 5330/5345/5355 |

| R3          | Вход синхронного сброса                                          |

| R4          | Вход асинхронного сброса фазового детектора и делителя частоты   |

| F3          | Выход последовательности 9/4                                     |

| F4          | Выход последовательностей 5315/5335                              |

| F5          | Выход последовательности 5335/5315                               |

| F6          | Выход последовательностей 5330/5345/5355                         |

| F7          | Выход последовательности 180/90                                  |

| F8          | Выход последовательности 15/1                                    |

| F9          | Выход последовательности 1000/1                                  |

| <u>F9</u>   | Выход последовательности 1000/999 (инверсный)                    |

## ФУНКЦИОНИРОВАНИЕ БЛОКА ФАЗОВОГО ДЕТЕКТОРА

Блок фазового детектора включает в себя:

- программируемые делители частоты;

- фазовый компаратор;

- формирователь сигнала готовности.

На входы СТ1 и СТ2 подаются импульсные последовательности генератора опорной частоты и генератора, управляемого напряжением соответственно.

Программируемые делители осуществляют деление частоты поступающих на их входы последовательностей импульсов.

Коэффициенты деления К1 и К2 программируемых делителей определяются значениями сигналов на шинах D1 и D2:

$$K_1 = 513 - \sum_{i=0}^8 D1[i] \cdot 2^i, \quad K_2 = 513 - \sum_{i=0}^8 D2[i] \cdot 2^i;$$

$D1[i], D2[i] \in \{0, 1\}$ .

Поделенные последовательности поступают на выходы F1 и F2 микросхемы, а также на входы фазового компаратора.

В случае, когда частота импульсов F1 больше частоты импульсов F2 ( $f_{F1} > f_{F2}$ ), на выходе A>B формируется последовательность импульсов, длительность которых равна величине рассогласования фаз между сигналами F1 и F2. При этом на выходе A<B будут формироваться импульсы, длительность которых не превышает 10 нс.

При  $f_{F1} < f_{F2}$  последовательность импульсов рассогласования фаз формируется на выходе A<B, на выходе A>B – импульсы длительностью не более 10 нс.

При  $f_{F1} = f_{F2}$  на обоих выходах A>B и A<B формируются импульсы длительностью не более 10 нс. При этом формируется сигнал готовности фазового детектора, который выдается на выход PPD.

Сигнал PPD формируется при условии, когда рассогласование между фронтами сигналов F2 и F1 находится в интервале  $\Delta = [-t_{CT1}; 2 t_{CT1}]$ , где  $t_{CT1}$  – длительность импульсов на входе СТ1.

## ФУНКЦИОНИРОВАНИЕ БЛОКА ФОРМИРОВАНИЯ ИМПУЛЬСНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ

Импульсные последовательности F3, F7 и F8 формируются из входной опорной последовательности СТ3 и имеют следующие значения периода повторения Т и скважности Q:

$$T^{F3} = 9 T^{CT3}, \quad Q^{F3} = 9/4;$$

$$T^{F7} = 180 T^{CT3}, \quad Q^{F7} = 2;$$

$$T^{F8} = 15 T^{CT3}, \quad Q^{F8} = 15;$$

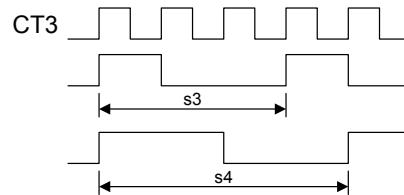

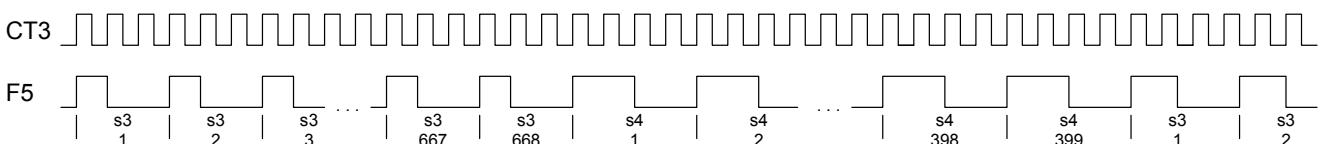

Основу последовательностей F4, F5 и F6 составляют «символы» s3 и s4, которые формируются из опорной последовательности СТ3:

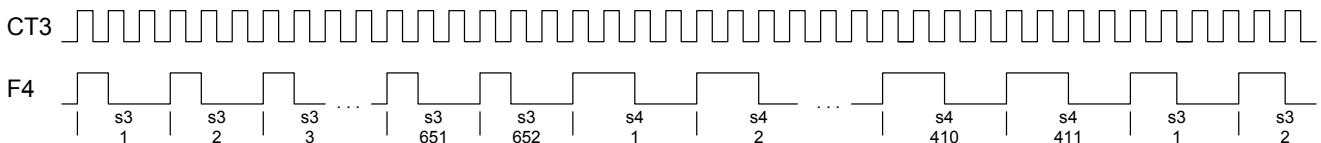

Последовательности F4, F5 и F6 представляют собой чередующиеся наборы из M «символов» s3 и N «символов» s4.

Значения M и N определяются значениями сигналов на входах CE1, CE2 и CE4 в соответствии с таблицами:

### последовательность F4

| CE1 | Код последовательности | M   | N   |

|-----|------------------------|-----|-----|

| 0   | 5315                   | 652 | 411 |

| 1   | 5335                   | 668 | 399 |

### последовательность F5

| CE2 | Код последовательности | M   | N   |

|-----|------------------------|-----|-----|

| 0   | 5335                   | 668 | 399 |

| 1   | 5315                   | 652 | 411 |

### последовательность F6

| CE4.2 | CE4.1 | Код последовательности | M   | N   |

|-------|-------|------------------------|-----|-----|

| 0     | 0     | -                      | -   | -   |

| 0     | 1     | 5330                   | 660 | 405 |

| 1     | 0     | 5345                   | 676 | 393 |

| 1     | 1     | 5355                   | 684 | 387 |

## ФУНКЦИОНИРОВАНИЕ БЛОКА ДЕЛЕНИЯ ЧАСТОТЫ

Блок деления частоты осуществляет преобразование входной последовательности СТ4 в выходную последовательность F9, имеющую следующие значения периода повторения Т и длительности импульса  $t_h$ :

$$T^{F9} = 1000 T^{CT4}, \quad t_h^{F9} = T^{CT4}.$$

Последовательность F9 выдается на выход микросхемы в прямой и инверсной фазе.

Пример формирования последовательности F4 при CE1 = 1

Пример формирования последовательности F5 при CE2 = 0