# Микросхема синтезатора частот с дробным коэффициентом деления 1508AC015, K1508AC015K, 1508AC01H4, K1508AC01H4

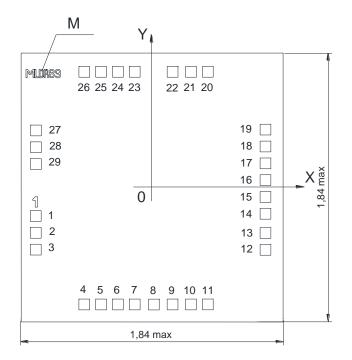

Вид сверху

ГГ – год выпуска НН – неделя выпуска

# Основные характеристики микросхемы:

- Основная частота до 12 ГГц;

- Программируемый прескалер 8/9, 4/5;

- Опорная частота до 250 МГц;

- Частота фазового детектора в целочисленном режиме до 150 МГц;

- Частота фазового детектора в дробном режиме до 70 МГц;

- Шаг основной частоты не более

1,04 Гц (26 разрядный сигма-дельта модулятор);

- Нормированный уровень фазовых шумов в целочисленном режиме не более минус 227 дБн/Гц;

- Нормированный уровень фликкер фазовых шумов в целочисленном режиме не более минус 118 дБн/Гц;

- Встроенная функция "предотвращение проскальзывания циклов";

- Напряжение питания от 3,0 до 3,6 В;

- Динамический ток потребления не более 130 мА;

- Температурный диапазон:

| Обозначение | Диапазон          |

|-------------|-------------------|

| 1508AC015   | минус 60 – 125 °C |

| K1508AC015  | минус 60 – 125 °C |

| K1508AC015K | 0 – 70°C          |

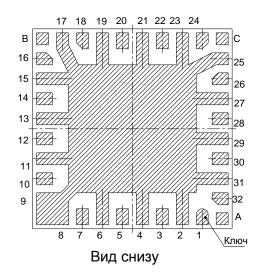

## Тип корпуса:

- 32-выводной металлокерамический корпус 5102.32-2К;

- микросхемы 1508AC01H4 и К1508AC01H4 поставляются в бескорпусном исполнении.

# Области применения микросхемы

Микросхема предназначена для построения блоков генераторов сигнала на основе фазовой автоподстройки частоты, которые могут быть применены:

- в базовых станциях для мобильного радио (GSM, PCS, DCS, CDMA);

- в беспроводных локальных сетях;

- в космической радиолокации.

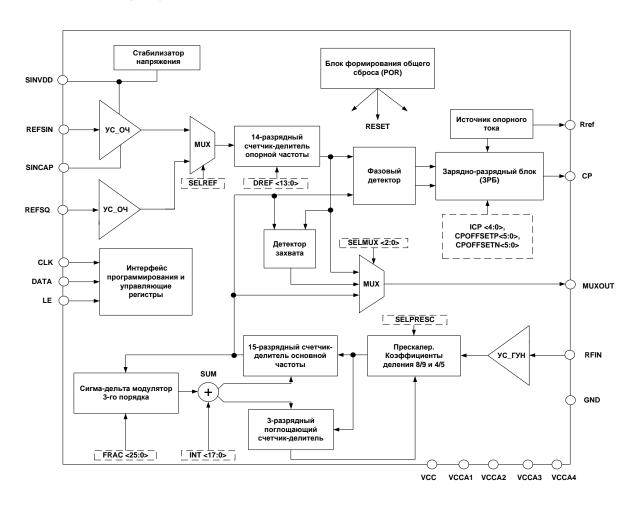

## 1 Структурная блок-схема микросхемы

-\_\_\_\_ <sup>;</sup> – управляющие разряды регистра выбора режима работы;

УС\_ОЧ – усилитель сигнала опорной частоты;

УС\_ГУН – усилитель сигнала основной частоты ГУН (генератор,

управляемый напряжением);

MUX – мультиплексор;

SUM – сумматор.

Рисунок 1 – Структурная блок-схема микросхемы

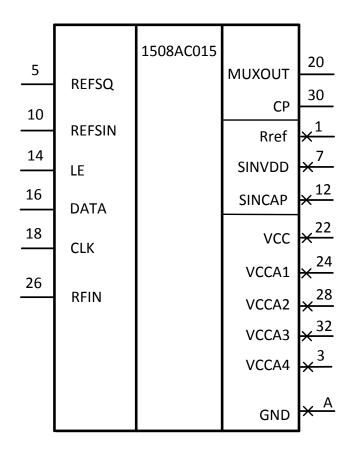

## 2 Условное графическое обозначение

А – Группа выводов: 2, 4, 6, 8, 9, 11, 13, 15, 17, 19, 21, 23, 25, 27, 29, 31, A, B, C

Рисунок 2 – Условное графическое обозначение

# 3 Описание выводов

Таблица 1 – Описание выводов

| Номер<br>вывода<br>корпуса | Номер<br>контактной<br>площадки<br>кристалла | Обозначение<br>вывода | Тип<br>вывода* | Функциональное назначение вывода                                                                                                                                                       |  |

|----------------------------|----------------------------------------------|-----------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1                          | 21                                           | Rref                  | -              | Вывод подключения резистора, задающего опорный ток                                                                                                                                     |  |

| 2                          | 22                                           | GND                   | -              | Общий**                                                                                                                                                                                |  |

| 3                          | 23                                           | VCCA4                 | -              | Питание усилителей сигналов и счетчика-<br>делителя опорной частоты, 3,3 В                                                                                                             |  |

| 4                          | _                                            | GND                   | -              | Общий**                                                                                                                                                                                |  |

| 5                          | 24                                           | REFSQ                 | Al             | Вход сигнала опорной частоты прямоугольной формы                                                                                                                                       |  |

| 6                          | 25                                           | GND                   | -              | Общий**                                                                                                                                                                                |  |

| 7                          | 26                                           | SINVDD                | -              | Выход для подключения внешней фильтрующей емкости стабилизатора напряжения питания усилителя сигнала опорной частоты синусоидальной формы                                              |  |

| 8                          | _                                            | GND                   | -              | Общий**                                                                                                                                                                                |  |

| 9                          | 27                                           | GND                   | -              | Общий**                                                                                                                                                                                |  |

| 10                         | 28                                           | REFSIN                | Al             | Вход сигнала опорной частоты синусоидальной формы                                                                                                                                      |  |

| 11                         | _                                            | GND                   | -              | Общий**                                                                                                                                                                                |  |

| 12                         | 29                                           | SINCAP                | -              | Выход для подключения внешней фильтрующей емкости усилителя сигнала опорной частоты синусоидальной формы                                                                               |  |

| 13                         | 1                                            | GND                   | -              | Общий**                                                                                                                                                                                |  |

| 14                         | 2                                            | LE                    | I              | Сигнал разрешения записи данных в управляющие регистры                                                                                                                                 |  |

| 15                         | _                                            | GND                   | -              |                                                                                                                                                                                        |  |

| 16                         | 3                                            | DATA                  | I              | Вход данных управляющего регистра                                                                                                                                                      |  |

| 17                         | _                                            | GND                   | -              | Общий**                                                                                                                                                                                |  |

| 18                         | 4                                            | CLK                   | I              | Сигнал тактовой частоты интерфейса программирования                                                                                                                                    |  |

| 19                         | 5                                            | GND                   | •              | Общий**                                                                                                                                                                                |  |

| 20                         | 6                                            | MUXOUT                | АО             | Программируемый выход счетчиков-<br>делителей основной и опорной частоты.<br>На выход поступает сигнал от источника,<br>определяемого значениями разрядов<br>SELMUX<1:0> регистра REG4 |  |

| 21                         | 7                                            | GND                   | •              | Общий**                                                                                                                                                                                |  |

| 22                         | 8                                            | VCC                   | -              | Питание цифровых блоков                                                                                                                                                                |  |

| 23                         | 9                                            | GND                   | -              | Общий**                                                                                                                                                                                |  |

| 24                         | 10, 11                                       | VCCA1                 | -              | Питание аналоговых ВЧ блоков 3,3 В                                                                                                                                                     |  |

| 25                         | _                                            | GND                   | -              | Общий**                                                                                                                                                                                |  |

| 26                         | 12                                           | RFIN                  | Al             | ВЧ вход прескалера (делителя основной частоты ГУН)                                                                                                                                     |  |

| 27                         | 13, 14                                       | GND                   | -              | Общий**                                                                                                                                                                                |  |

| 28                         | 15                                           | VCCA2                 | -              | Питание зарядно-разрядного блока и фазового детектора, 3,3 В                                                                                                                           |  |

| Номер<br>вывода<br>корпуса | Номер<br>контактной<br>площадки<br>кристалла | Обозначение<br>вывода | Тип<br>вывода* | Функциональное назначение вывода                                            |

|----------------------------|----------------------------------------------|-----------------------|----------------|-----------------------------------------------------------------------------|

| 29                         | 16                                           | GND                   | ı              | Общий**                                                                     |

| 30                         | 17                                           | СР                    | АО             | Выход зарядно-разрядного блока для подключения к внешнему петлевому фильтру |

| 31                         | 18, 19                                       | GND                   | ı              | Общий**                                                                     |

| 32                         | 20                                           | VCCA3                 |                | Питание источника опорного тока, 3,3 В                                      |

| A, B, C                    | _                                            | GND                   |                | Общий**                                                                     |

<sup>\*</sup> Обозначение типа выводов:

I – цифровой вход;

AI – аналоговый вход;

АО – аналоговый выход.

<sup>\*\*</sup> Вывод соединен с обратной стороной и крышкой микросхемы

#### 4 Указания по применению и эксплуатации

При ремонте аппаратуры и измерении параметров микросхем замену микросхем необходимо проводить только при отключенных источниках питания.

Инструмент для пайки (сварки) и монтажа не должен иметь потенциал, превышающий 0,3 В относительно шины "Общий".

Не используемые входы микросхем должны быть подключены к напряжению питания Ucc или к шине «Общий» GND.

Запрещается подведение каких-либо электрических сигналов (в том числе шин "Питание", "Общий") к выходам микросхем, не используемым согласно схеме электрической.

Площадки A, B, C, крышка, металлизированная площадка обратной стороны микросхем электрически соединены с выводами «Общий».

Порядок подачи и снятия напряжения питания и входных сигналов на микросхему должен быть следующим:

- подача (включение микросхемы): общий, питание, входные сигналы;

- снятие (выключение микросхемы): в обратном порядке.

#### 5 Описание функционирования микросхемы

Микросхема представляет собой часть синтезатора частоты, которая в сочетании с внешним управляемым генератором и петлевым фильтром образует законченную петлю ФАПЧ и предназначена для построения блоков высокочастотных генераторов сигнала на основе фазовой автоподстройки частоты, которые могут быть применены:

- в базовых станциях для мобильного радио (GSM, PCS, DCS, CDMA);

- в беспроводных локальных сетях;

- в космической радиолокации.

Синтезатор имеет дробный делитель основной частоты, построенный на основе 26-разрядного сигма-дельта модулятора 3 порядка.

Синтезатор может работать в дробном и целочисленном режимах в зависимости от сигнала **SYNTMOD** управляющего регистра:

1. Если **SYNTMOD = <1>** микросхема работает в дробном режиме, частота управляемого генератора определяется по формуле

$$F = \frac{F_{REF}}{DREF} \left( INT + \frac{FRAC}{2^{26}} \right), \tag{1}$$

где  $F_{ref}$  – частота опорного сигнала;

DREF - коэффициент деления опорной частоты;

INT – целая часть коэффициента деления основной частоты;

FRAC – числитель дробной части коэффициента деления основной частоты.

2. Если **SYNTMOD = <0>** микросхема работает в целочисленном режиме, и частота управляемого генератора определяется по формуле

$$F = F_{REF} \frac{INT}{DREF}.$$

(2)

Значения *INT*, *FRAC*, *DREF* задаются соответствующими полями, управляющими регистрами REG1÷REG3.

Микросхема может быть переведена в режим **пониженного энергопотребления** с отключением всех внутренних блоков путем установки управляющего сигнала **POWERDOWN = 1**. В рабочем режиме **POWERDOWN = 0**.

В микросхеме встроен блок опорного тока, основанный на внешнем резисторе, который подключается между выводом Rref и «Общий». Рекомендованное значение резистора составляет 1,13 кОм  $\pm$  1 %. Высокая точность задающего резистора необходима для обеспечения значений выходного тока зарядно-разрядного блока (ЗРБ). В приложениях, где не критично небольшое отклонение выходного тока ЗРБ от указанных значений, возможна установка задающего резистора номиналом 1,1 кОм  $\pm$  10 %.

Блок источника опорного тока включается сигналом **ENBIAS = 1**.

При подаче напряжения питания до загрузки управляющих регистров микросхема находится в режиме пониженного энергопотребления. Состояние выхода MUXOUT в этом режиме не определено.

#### 5.1 Тракт делителя основной частоты

Делитель основной частоты построен по схеме двухмодульного прескалера с основным и поглощающим счетчиками. В зависимости от диапазона основой частоты должен быть выбран один из двух режимов работы прескалера: 8/9 или 4/5. От выбора режима работы прескалера будут также зависеть значения INT (Таблица 2). Выбор прескалера осуществляется управляющим сигналом **SELPRESC**. Включение тракта делителя основной частоты осуществляется установкой **ENHDIV = 1**.

Таблица 2 – Значения целой части коэффициента деления основной частоты INT в зависимости от выбора коэффициентов деления прескалера

| Основная частота ГУН, ГГц | •   | SELPRESC | INT <sub>min</sub><br>(дробный<br>режим) | INT <sub>max</sub><br>(дробный<br>режим) | INT <sub>min</sub><br>(целочислен-<br>ный режим) | INT <sub>max</sub><br>(целочислен-<br>ный режим) |

|---------------------------|-----|----------|------------------------------------------|------------------------------------------|--------------------------------------------------|--------------------------------------------------|

| 6÷12                      | 8/9 | 0        | 59                                       | 262139                                   | 56                                               | 262143                                           |

| < 6                       | 4/5 | 1        | 27                                       | 131067                                   | 24                                               | 131071                                           |

Дробный коэффициент деления делителя реализуется при помощи 26-разрядного сигма-дельта модулятора 3-го порядка. Числитель дробной части коэффициента деления задается шиной FRAC<25:0>.

Сигналы **DSMSINEN**, **DSMSQEN**, **DSMCLKSET** используются исключительно в тестовых целях проверки работоспособности сигма-дельта модулятора. В рабочем режиме работы данные сигналы должны быть установлены в 0.

#### 5.2 Тракт делителя опорной частоты

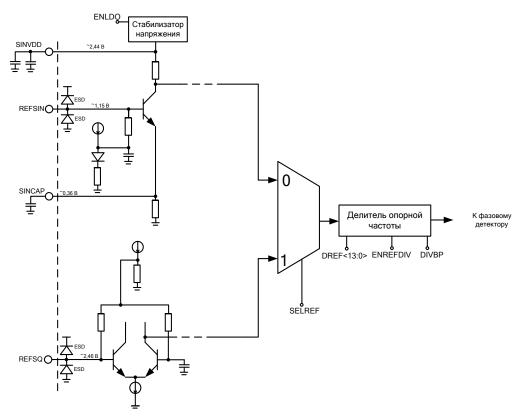

На рисунке представлена упрощенная схема входных цепей тракта опорной частоты.

Рисунок 3 – Структурная схема тракта делителя опорной частоты

В качестве опорной частоты для синтезатора могут использоваться источники сигналов синусоидальной или прямоугольной формы в диапазоне частот от 0 до 250 МГц. В микросхеме используются два независимых усилителя опорной частоты, оптимизированных под соответствующий тип сигнала. Опорный сигнал синусоидальной формы подавать на вход **REFSIN**, прямоугольный – на вход **REFSQ**.

Для питания усилителя синусоидального сигнала используется внутренний Это напряжение стабилизатор напряжения с уровнем напряжения 2,44 В. фильтруется вывод SINVDD. внешними емкостями через Эквивалентное последовательное сопротивление подключаемых емкостей быть должно не более 1,5 Ом для обеспечения устойчивости стабилизатора. Стабилизатор имеет индивидуальный сигнал включения ENLDO.

Усилители включаются установкой сигналов **ENSIN** и **ENSQ** в 1. Выбор используемого усилителя осуществляется внутренним мультиплексором по сигналу **SELREF**. Если задействован буфер синусоидального сигнала, необходимо установить **SELREF = 0**, если задействован буфер прямоугольного сигнала — **SELREF = 1**. Делитель опорной частоты включается установкой **ENREFDIV = 1**.

Установкой **DIVBP = 1** возможно пропустить сигнал опорной частоты в обход делителя, но при этом оставить делитель работающим. Этот режим используется исключительно в тестовых целях. Коэффициент деления делителя опорной частоты задается на шине **DREF<13:0>.**

Значения управляющих битов тракта опорной частоты в рабочем режиме в зависимости от выбранного усилителя входного сигнала приведены в таблице.

Таблица 3 – Значения управляющих битов тракта опорной частоты в рабочем режиме в зависимости от выбранного усилителя входного сигнала

| Режим работы                         | ENLLDO | ENSIN | ENSQ | ENREFDIV | SELREF |

|--------------------------------------|--------|-------|------|----------|--------|

| Вход сигнала<br>синусоидальной формы | 1      | 1     | 0    | 1        | 0      |

| Вход сигнала прямоугольной формы     | 0      | 0     | 1    | 1        | 1      |

#### 5.3 Зарядно-разрядный блок и фазовый детектор

3РБ представляет собой источник втекающего и вытекающего тока, переключаемый сигналами фазового детектора. ЗРБ включается установкой **ENCP = 1**.

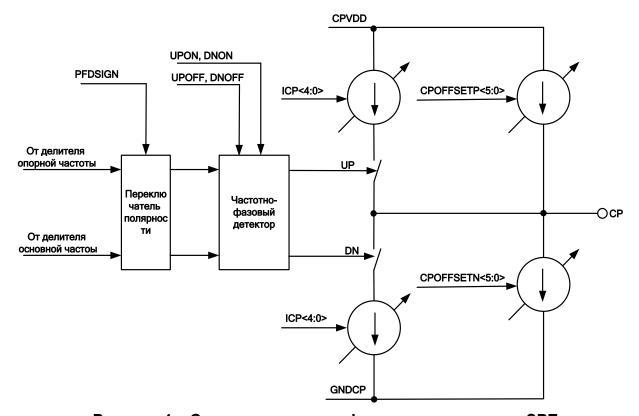

Структурная схема фазового детектора и ЗРБ приведена на рисунке .

Рисунок 4 – Структурная схема фазового детектора и ЗРБ

Шиной ICP<4:0> устанавливается значение выходного тока 3PБ по формуле

$$I_{cp} = 125 \text{ MKA}(1 + ICP),$$

(3)

где *ICP* – REG <4:0>.

Таким образом, можно установить значение выходного тока ЗРБ в диапазоне от 0,125 до 4 мА. Установкой сигнала **PFDSIGN = 1** можно при необходимости инвертировать полярность фазового детектора.

Сигналами **DNON**, **DNOFF**, **UPON**, **UPOFF** устанавливаются тестовые режимы работы 3PБ в соответствии с таблицей . В обычном режиме работы данные сигналы необходимо устанавливать равными 0.

| DNON | DNOFF | UPON | UPOFF | Режим                                                     |

|------|-------|------|-------|-----------------------------------------------------------|

| 1    | 0     | 0    | 1     | Включение вытекающего тока ЗРБ                            |

| 0    | 1     | 1    | 0     | Включение втекающего тока ЗРБ                             |

| 1    | 0     | 1    | 0     | Включение втекающего и вытекающего токов ЗРБ одновременно |

| 0    | 1     | 0    | 1     | Выключение токов ЗРБ (на выходе ЗРБ состояние – z)        |

#### Оптимальный ток смещения ЗРБ

Вследствие нелинейности передаточной характеристики ЗРБ и фазового детектора вблизи нулевой разности фаз входных сигналов в дробном режиме работы возникает непредсказуемо большое повышение фазового шума внутри полосы пропускания ФАПЧ. Для уменьшения данного эффекта в дробном режиме необходимо смещение области работы детектора в зону большей линейности. Это достигается введением постоянно включенной добавки к выходному току ЗРБ. Добавка может быть втекающая и вытекающая. Смещение области работы детектора уменьшает описанный эффект, однако увеличивает вклад собственного шума источников тока ЗРБ в общий фазовый шум ФАПЧ и увеличивает уровень паразитных сигналов на частоте сравнения ФАПЧ (reference spurs). Существует оптимальное значение смещающей добавки к выходному току ЗРБ Іср оffset ортітим, которое определяется по формуле

$$I_{cp\ offset\ optimum} = \gamma \frac{I_{cp}}{INT},\tag{4}$$

где  $\gamma = 2...4$ ;

$I_{cp}$  — установленное значение выходного тока 3РБ;

INT – установленное значение целой части коэффициента деления основной частоты.

Величина смещающей добавки задается значением регистров CPOFFSETP <5:0>, CPOFFSETN <5:0> при установленном состоянии ENOFFSETCP = 1 и определяется по формуле

$$I_{cp\ offset\ p,n}=6,25\ \text{мкA}*CPOFFSET_{P,N},$$

(5)

где **CPOFFSET p – REG2 <23:18>**; **CPOFFSET n – REG2 <29:24>**.

Диапазон возможных значений смещающей добавки от 0 до 383,75 мкА. Выбор оптимального направления тока смещающей добавки (втекающий или вытекающий) завит от технологического разбора и может выбираться пользователем.

При работе в целочисленном режиме смещающую добавку необходимо отключать установкой ENOFFSETCP = 0.

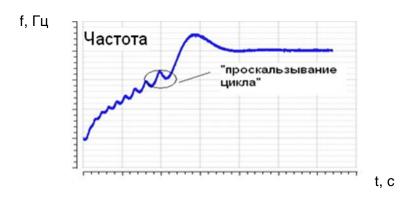

# 5.4 Функция предотвращения «проскальзывания» циклов (CSP – Cycle Slip Prevention)

Для данного класса систем ФАПЧ характерно «волнообразное» поведение основной частоты при перестройке с одной частоты на другую, что называют «проскальзыванием» циклов (Рисунок 5). Эффект связан с периодическим характером передаточной характеристики фазового детектора, в результате которого происходит периодический сброс фазовой ошибки, накопленной к определенному моменту времени. Эффект наблюдается в случае, если частота работы фазового детектора много больше полосы пропускания петли ФАПЧ. Как следствие, может сильно увеличивать время перестройки ФАПЧ.

Рисунок 5 – Переходный процесс в петле ФАПЧ с «проскальзыванием» циклов

В микросхеме реализован предотвращающий эффект механизм, «проскальзывания». определенные времени ПО специальным моменты внутренним сигналам происходит прибавление или вычитание к текущему коэффициенту деления основной частоты величины DN <14:0> (REG 1 <22:14>). Этим предотвращается полностью или минимизируется потеря фазовой ошибки. Оптимальная величина DN лежит в пределах (5 – 10) % от INT. Функция задействуется установкой **ENCSP = 1**.

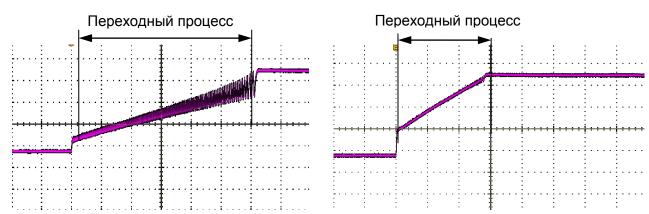

Рисунок 6 – Осциллограмма переходного процесса петли ФАПЧ с выключенной функцией CSP

Рисунок 7 – Осциллограмма переходного процесса петли ФАПЧ с включенной функцией CSP. DN=0,1·INT

На рисунках и для сравнения представлены осциллограммы переходного процесса ФАПЧ с включенной выключенной фикцией CSP. Как видно из рисунков,

включение данной функции сокращает время переходного процесса примерно в 2 раза.

#### 5.5 Детектор захвата

Для конфигурации выхода MUXOUT в качестве детектора захвата петли ФАПЧ необходимо записать регистр SELMUX=<1 X X> в соответствии с таблицей .

Детектор захвата выдает флаг захвата петли ФАПЧ на вывод MUXOUT, если **SELMUX = <1 X X>** (Таблица 5), когда разность фаз между входными сигналами фазового детектора становиться меньше порога, задаваемого шиной LDPT<1:0> и не превышает этот порог на протяжении 128 тактов частоты сравнения. Когда разность фаз становиться больше порога, детектор сбрасывает сигнал захвата в 0. Для корректной работы детектора должен быть выбран оптимальный порог срабатывания в зависимости от основной частоты синтезатора и режима работы (Таблица 6).

Таблица 5 – Сигналы управления состоянием выхода MUXOUT

| SELMUX<2:0> | Сигнал на выводе MUXOUT         |

|-------------|---------------------------------|

| 000         | Выход делителя опорной частоты  |

| 001         | Выход делителя основной частоты |

| 010         | Высокий логический уровень      |

| 011         | Низкий логический уровень       |

| 1XX         | Выход детектора захвата         |

Таблица 6 – Оптимальное значение LDPT в зависимости от диапазона основной частоты

| Основная частота,<br>ГГц | Режим работы  | Оптимальное<br>значение LDPT<1:0> | Номинальное<br>значение пороговой<br>разности фаз, нс |

|--------------------------|---------------|-----------------------------------|-------------------------------------------------------|

| 1–12                     | дробный       | <11>                              | 4,5                                                   |

| 0,75–1                   | дробный       | <10>                              | 5,5                                                   |

| 0,5–0,75                 | дробный       | <01>                              | 8                                                     |

| 0,1–0,5                  | дробный       | <00>                              | 35                                                    |

| любая частота            | целочисленный | x                                 | 1,6                                                   |

#### *5.5.1 Вывод MUXOUT*

Вывод MUXOUT может быть сконфигурирован в зависимости от значения сигнала управляющего регистра **SELMUX<1:0>** в соответствии с таблицей .

При переводе микросхемы в режим пониженного энергопотребления установкой POWERDOWN = 1 состояние выхода MUXOUT не определено.

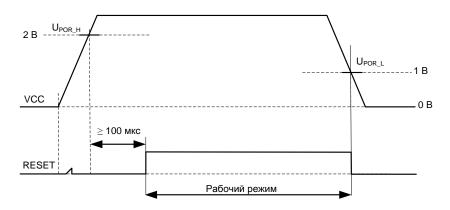

#### 5.6 Схема общего сброса при включении питания

Блок формирования общего сброса (POR – Power-On Reset) удерживает цифровую часть микросхемы в состоянии общего сброса, пока внутренний сигнал RESET имеет состояние логического нуля.

Временная диаграмма процедуры включения и выключения микросхемы при подаче и снятии питающего напряжения приведена на рисунке.

При подаче напряжения питания микросхема войдет в рабочий режим, когда напряжение на входе питания цифровых блоков VCC превысит пороговое напряжения включения UPOR\_H, и пройдет время не менее 100 мкс. До этого момента цифровая часть микросхемы будет находиться в состоянии сброса. При снятии питающего напряжения с вывода VCC сброс наступит при достижении уровня порогового напряжения отключения UPOR\_L. Уровень напряжения на остальных выводах питания не имеет значения.

Рисунок 8 – Временная диаграмма процедуры включения микросхемы при подаче питающего напряжения

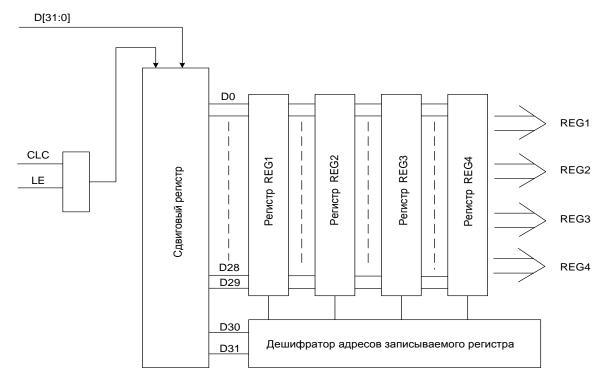

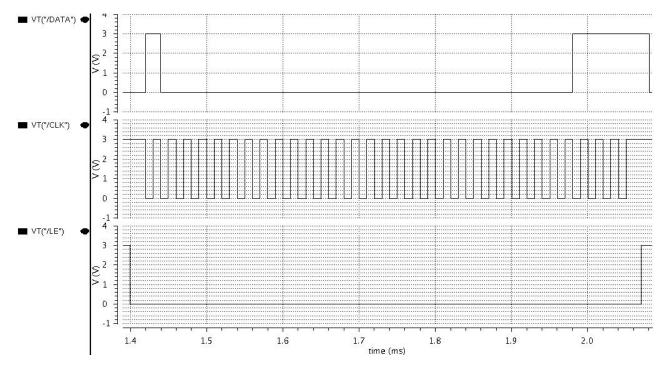

#### 5.7 Интерфейс программирования и описание регистров управления

#### 5.7.1 Выбор режима работы микросхемы синтезатора частот

Выбор режима работы микросхемы синтезатора частот производится путем программирования ее регистров управления через интерфейс программирования.

Загрузка данных рабочего режима работы синтезатора частот, а также данных для различных тестовых режимов производятся через последовательный интерфейс микросхемы (выводы CLK, DATA, LE).

Интерфейс состоит из 32-разрядного сдвигового регистра загрузки данных и четырех 30-разрядных регистров хранения управляющих данных (регистров управления), хранящих информацию о конфигурации микросхемы (Рисунок 9).

Рисунок 9 – Структурная схема интерфейса программирования и регистров управления

Два старших разряда сдвигового регистра DATA <31 и 30> определяют адрес выбранного при программировании управляющего регистра (Таблица 7).

| DATA<30> | Номер регистра     |

|----------|--------------------|

| 0        | <b>REG1</b> <29:0> |

| 1        | <b>REG2</b> <29:0> |

| 0        | <b>REG3</b> <29:0> |

|          | 0<br>1<br>0        |

1

Таблица 7 – Адреса управляющих регистров REG

#### 5.7.2 Порядок загрузки данных в регистры управления

Перед началом загрузки данных необходимо обеспечить начальное состояние входных сигналов: DATA = <0», LE = <1» и CLK = <1».

Ввод данных осуществляется по 32 бита за один цикл. Загрузка данных в сдвиговый регистр осуществляется после подачи низкого логического уровня на вход LE по переднему фронту сигнала CLK. Установка данных должна быть произведена в любое время до этого события.

Загрузка данных начинается с двух старших разрядов, определяющих номер регистра хранения управляющих данных. Далее, начиная со старшего бита, следуют данные, загружаемые в управляющий регистр.

Порядок следования загрузочных данных: DATA<31>, DATA<30>, DATA<29>, ......, DATA<0>

**REG4**<29:0>

После подачи на вход LE логической единицы данные из сдвигового регистра переписываются в выбранный регистр. Сигналы интерфейса программирования в режиме загрузки регистров приведены на рисунке 10.

Рисунок 10 – Сигналы интерфейса программирования в режиме загрузки регистров

#### 5.7.3 Описание регистров управления

Назначение разрядов регистров управления REG1÷REG4 приведено в таблице 8.

Таблица 8 – Описание разрядов регистров управления REG1÷REG4

| Биты | Обозначение      | Предназначение                                                   | Определение                                  |  |  |  |

|------|------------------|------------------------------------------------------------------|----------------------------------------------|--|--|--|

|      | Регистр 1 (REG1) |                                                                  |                                              |  |  |  |

| 0    | DREF<0>          |                                                                  |                                              |  |  |  |

| 1    | DREF<1>          |                                                                  |                                              |  |  |  |

| 2    | DREF<2>          |                                                                  |                                              |  |  |  |

| 3    | DREF<3>          |                                                                  |                                              |  |  |  |

| 4    | DREF<4>          |                                                                  |                                              |  |  |  |

| 5    | DREF<5>          |                                                                  |                                              |  |  |  |

| 6    | DREF<6>          | DREF                                                             | Коэффициент деления                          |  |  |  |

| 7    | DREF<7>          | DREF                                                             | опорной частоты                              |  |  |  |

| 8    | DREF<8>          |                                                                  |                                              |  |  |  |

| 9    | DREF<9>          |                                                                  |                                              |  |  |  |

| 10   | DREF<10>         |                                                                  |                                              |  |  |  |

| 11   | DREF<11>         |                                                                  |                                              |  |  |  |

| 12   | DREF<12>         |                                                                  |                                              |  |  |  |

| 13   | DREF<13>         |                                                                  |                                              |  |  |  |

| 14   | DN<0>            |                                                                  |                                              |  |  |  |

| 15   | DN<1>            |                                                                  |                                              |  |  |  |

| 16   | DN<2>            |                                                                  |                                              |  |  |  |

| 17   | DN<3>            |                                                                  |                                              |  |  |  |

| 18   | DN<4>            |                                                                  |                                              |  |  |  |

| 19   | DN<5>            |                                                                  | Величина динамической                        |  |  |  |

| 20   | DN<6>            |                                                                  | изменяемой добавки к<br>целой части делителя |  |  |  |

| 21   | DN<7>            | DN                                                               | основной частоты для                         |  |  |  |

| 22   | DN<8>            |                                                                  | реализации функции<br>"предотвращение        |  |  |  |

| 23   | DN<9>            |                                                                  | проскальзывания циклов"                      |  |  |  |

| 24   | DN<10>           |                                                                  |                                              |  |  |  |

| 25   | DN<11>           |                                                                  |                                              |  |  |  |

| 26   | DN<12>           |                                                                  |                                              |  |  |  |

| 27   | DN<13>           |                                                                  |                                              |  |  |  |

| 28   | DN<14>           |                                                                  |                                              |  |  |  |

| 29   | ENCSP            | Сигнал включения функции «Предотвращение проскальзывания циклов» | 0 — выкл.<br>1 — вкл.                        |  |  |  |

| Биты | Обозначение  | Предназначение   | Определение                                        |

|------|--------------|------------------|----------------------------------------------------|

|      |              | Регистр 2 (REG2) | •                                                  |

| 0    | INT<0>       |                  |                                                    |

| 1    | INT<1>       |                  |                                                    |

| 2    | INT<2>       |                  |                                                    |

| 3    | INT<3>       |                  |                                                    |

| 4    | INT<4>       |                  |                                                    |

| 5    | INT<5>       |                  |                                                    |

| 6    | INT<6>       |                  |                                                    |

| 7    | INT<7>       |                  |                                                    |

| 8    | INT<8>       | INT              | Целая часть коэффициента                           |

| 9    | INT<9>       | INI              | деления основной частоты                           |

| 10   | INT<10>      |                  |                                                    |

| 11   | INT<11>      |                  |                                                    |

| 12   | INT<12>      |                  |                                                    |

| 13   | INT<13>      |                  |                                                    |

| 14   | INT<14>      |                  |                                                    |

| 15   | INT<15>      |                  |                                                    |

| 16   | INT<16>      |                  |                                                    |

| 17   | INT<17>      |                  |                                                    |

| 18   | CPOFFSETP<0> |                  |                                                    |

| 19   | CPOFFSETP<1> |                  | Величина постоянной                                |

| 20   | CPOFFSETP<2> | CPOFFSETP        | добавки к вытекающему                              |

| 21   | CPOFFSETP<3> | CPOFFSETP        | току зарядно-разрядного                            |

| 22   | CPOFFSETP<4> |                  | блока                                              |

| 23   | CPOFFSETP<5> |                  |                                                    |

| 24   | CPOFFSETN<0> |                  |                                                    |

| 25   | CPOFFSETN<1> |                  |                                                    |

| 26   | CPOFFSETN<2> | CPOFFSETN        | Величина постоянной                                |

| 27   | CPOFFSETN<3> | CFOFFSEIN        | добавки к втекающему току зарядно-разрядного блока |

| 28   | CPOFFSETN<4> |                  | han the alternative and a second                   |

| 29   | CPOFFSETN<5> |                  |                                                    |

| Биты | Обозначение | Предназначение                                     | Определение                                      |

|------|-------------|----------------------------------------------------|--------------------------------------------------|

|      |             | Регистр 3 (REG3)                                   |                                                  |

| 0    | FRAC<0>     |                                                    |                                                  |

| 1    | FRAC<1>     |                                                    |                                                  |

| 2    | FRAC<2>     |                                                    |                                                  |

| 3    | FRAC<3>     |                                                    |                                                  |

| 4    | FRAC<4>     |                                                    |                                                  |

| 5    | FRAC<5>     |                                                    |                                                  |

| 6    | FRAC<6>     |                                                    |                                                  |

| 7    | FRAC<7>     |                                                    |                                                  |

| 8    | FRAC<8>     |                                                    |                                                  |

| 9    | FRAC<9>     |                                                    |                                                  |

| 10   | FRAC<10>    |                                                    |                                                  |

| 11   | FRAC<11>    |                                                    |                                                  |

| 12   | FRAC<12>    | FRAC                                               | Числитель дробной части                          |

| 13   | FRAC<13>    | FRAC                                               | коэффициента деления основной частоты            |

| 14   | FRAC<14>    |                                                    |                                                  |

| 15   | FRAC<15>    |                                                    |                                                  |

| 16   | FRAC<16>    |                                                    |                                                  |

| 17   | FRAC<17>    |                                                    |                                                  |

| 18   | FRAC<18>    |                                                    |                                                  |

| 19   | FRAC<19>    |                                                    |                                                  |

| 20   | FRAC<20>    |                                                    |                                                  |

| 21   | FRAC<21>    |                                                    |                                                  |

| 22   | FRAC<22>    |                                                    |                                                  |

| 23   | FRAC<23>    |                                                    |                                                  |

| 24   | FRAC<24>    |                                                    |                                                  |

| 25   | FRAC<25>    |                                                    |                                                  |

| 26   | SELPRESC    | Выбор используемого прескалера                     | 0 – прескалер 8/9<br>1 – прескалер 4/5           |

| 27   | SELREF      | Выбор источника опорной частоты                    | 0 – синус<br>1 – прямоугольный сигнал            |

| 28   | SYNTMOD     | Режим работы синтезатора                           | 0 – целочисленный<br>1 – дробный                 |

| 29   | PFDSIGN     | Выбор полярности<br>сигналов фазового<br>детектора | 0 – прямая полярность<br>1 – обратная полярность |

| Биты | Обозначение | Предназначение                                                                                                  | Определение                                                                                                                                                                       |

|------|-------------|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | •           | Регистр (REG4)                                                                                                  |                                                                                                                                                                                   |

| 0    | ICP<0>      |                                                                                                                 |                                                                                                                                                                                   |

| 1    | ICP<1>      |                                                                                                                 |                                                                                                                                                                                   |

| 2    | ICP<2>      | ICP                                                                                                             | Значение выходного тока зарядно-разрядного блока                                                                                                                                  |

| 3    | ICP<3>      |                                                                                                                 | зарядно-разрядного олока                                                                                                                                                          |

| 4    | ICP<4>      |                                                                                                                 |                                                                                                                                                                                   |

| 5    | резерв      |                                                                                                                 |                                                                                                                                                                                   |

| 6    | резерв      |                                                                                                                 |                                                                                                                                                                                   |

| 7    | LDPT<0>     |                                                                                                                 | LDPT<1:0>                                                                                                                                                                         |

| 8    | LDPT<1>     | LDPT                                                                                                            | Величина пороговой разности фаз входных сигналов фазового детектора, при которой детектируется захват петли ФАПЧ в дробном режиме: 00 – 35 нс 01 – 8,5 нс 10 – 5,5 нс 11 – 4,5 нс |

| 9    | ENOFFSETCP  | Включение добавочного                                                                                           | 1 — вкл                                                                                                                                                                           |

|      |             | тока ЗРБ                                                                                                        | 0 — выкл                                                                                                                                                                          |

| 10   | резерв      |                                                                                                                 |                                                                                                                                                                                   |

| 11   | DNON        |                                                                                                                 |                                                                                                                                                                                   |

| 12   | DNOFF       | проверки зарядно-                                                                                               | Таблица 4                                                                                                                                                                         |

| 13   | UPON        | разрядного блока                                                                                                |                                                                                                                                                                                   |

| 14   | UPOFF       | D. C.                                                                                                           |                                                                                                                                                                                   |

| 15   | ENBIAS      | Выбор режима работы источника опорного тока                                                                     | 0 — выкл.<br>1 — вкл.                                                                                                                                                             |

| 16   | ENCP        | Выбор режима работы<br>зарядно-разрядного блока                                                                 | 0 — выкл.<br>1 — вкл.                                                                                                                                                             |

| 17   | ENHDIV      | Выбор режима работы делителя основной частоты                                                                   | 0 – выкл.<br>1 – вкл.                                                                                                                                                             |

| 18   | ENLDO       | Выбор режима работы<br>стабилизатора напряжения<br>усилителя сигнала опорной<br>частоты синусоидальной<br>формы | 0 – выкл. (напряжение питания на усилитель необходимо подавать через вывод SINVDD) 1 – вкл.                                                                                       |

| 19   | ENSIN       | Выбор режима работы усилителя сигнала опорной частоты синусоидальной формы                                      | 0 — выкл.<br>1 — вкл.                                                                                                                                                             |

| 20   | ENSQ        | Выбор режима работы усилителя сигнала опорной частоты прямоугольной формы                                       | 0 — выкл.<br>1 — вкл.                                                                                                                                                             |

| 21 | DSMSINEN  | Разрешение использования сигнала опорной частоты синусоидальной формы в качестве тактовой частоты дельта-сигма модулятора | 0 — выкл.<br>1 — вкл.                                                                                                     |

|----|-----------|---------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| 22 | DSMSQEN   | Разрешение использования сигнала опорной частоты прямоугольной формы в качестве тактовой частоты дельта-сигма модулятора  | 0 — выкл.<br>1 — вкл.                                                                                                     |

| 23 | DSMCLKSET | Выбор источника тактового сигнала дельта-сигма модулятора                                                                 | 0 – сигнал опорной частоты синусоидальной формы 1 – сигнал опорной частоты прямоугольной формы                            |

| 24 | ENREFDIV  | Выбор режима работы делителя опорной частоты                                                                              | 0 — выкл.<br>1 — вкл.                                                                                                     |

| 25 | DIVBP     | Разрешение прямого прохождения сигнала опорной частоты через делитель                                                     | 0 — выкл.<br>1 — вкл.                                                                                                     |

| 26 | SELMUX<0> |                                                                                                                           | SELMUX<2:0>                                                                                                               |

| 27 | SELMUX<1> | 1                                                                                                                         | 000-выход делителя сигнала опорной частоты                                                                                |

| 28 | SELMUX<2> | Выбор типа выходного<br>сигнала на выводе<br>MUXOUT                                                                       | 001 – выход делителя сигнала основной частоты 010 – логическая 1 011 – логический 0 1XX – Выход сигнала детектора захвата |

| 29 | POWERDOWN | Режим пониженного энергопотребления микросхемы                                                                            | 0 — выкл.<br>1 — вкл.                                                                                                     |

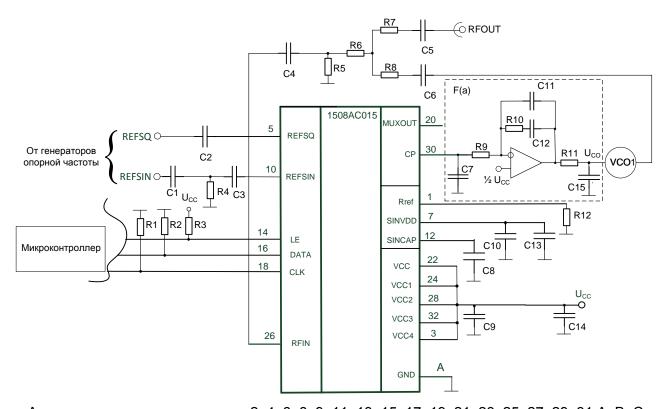

#### RFOUT C5 ∐R5 C4 C<sub>6</sub> 1508AC015 F(z) 20 иихоит $U_{\text{CO}}$ R10 REFSQ O REESO VCO' 30 От генераторов СР R9 C2 опорной частоть 10 C9] **REFSIN** O REFSIN Rref ∏R11 SINVDD ∏R1 ∏R2 ∏R3 14 12 SINCAP C10 16 Микроконтроллер 18 VCC C7 CLK 24 VCCA1 28 VCCA2 VCCA3 3 26 VCCA4 RFIN

#### 6 Типовые схемы включения микросхемы

А – группа выводов 2, 4, 6, 8, 9, 11, 13, 15, 17, 19, 21, 23, 25, 27, 29, 31, A, B, C; C1 – C14 — конденсаторы емкостью: C1 = C7 = C10 = 10 нФ; C2 = C4 = C5 = C6 = 100 пФ, C3 = C14 = 100 нФ, C8 = 10 пФ, C12 = 1 мкФ; С9, C11, C13 — емкости выбираются в зависимости от желаемых параметров петли

GND

С9, С11, С13 – емкости выбираются в зависимости от желаемых параметров петли ФАПЧ;

F(z) – петлевой фильтр ФАПЧ;

R1 - R11 — резисторы сопротивлением, R1 = R2 = R3 = 100 кОм, R4 = 91 Ом, R5 = 51 Ом. R6 = R7 = R8 = 18 Ом. R11 = 1.07 кОм  $\pm 1$  %:

R9, R10 – сопротивления выбираются в зависимости от желаемых параметров петли ФАПЧ:

U<sub>CO</sub> – управляющее напряжение;

VCO1 – генератор управляемый напряжением.

При подаче опорной частоты только на один из входов (REFSQ или REFSIN) незадействованный вход должен быть подключен к шине «Общий» через конденсатор емкостью 10 пФ.

Допускается подача опорной частоты на оба входа одновременно. Выбор входа подачи опорной частоты см. п. 5.2 «Тракт делителя опорной частоты».

# Рисунок 11 – Типовая схема включения микросхемы с пассивным петлевым фильтром

А — группа выводов 2, 4, 6, 8, 9, 11, 13, 15, 17, 19, 21, 23, 25, 27, 29, 31 A, B, C; C1 — C15 — конденсаторы емкостью: C1 = C8 = C10 = 10 нФ, C2 = C4 = C5 = C6 = 100 пФ, C3 = C14 = 100 нФ, C9 = 10 пФ, C13 = 1 мкФ,

C2 = C4 = C5 = C6 = 100 пФ, C3 = C14 = 100 нФ, C9 = 10 пФ, C13 = 1 мкФ, C7, C11, C12, C15 – емкости выбираются в зависимости от желаемых параметров петли ФАПЧ;

F(a) – активный петлевой фильтр ФАПЧ;

R1 - R12 — резисторы сопротивлением: R1 = R2 = R3 = 100 кОм, R4 = 91 Ом,

$R5 = 51 \text{ OM}, R6 = R7 = R8 = 18 \text{ OM}, R12 = 1,07 \text{ kOM} \pm 1 \%,$

R9, R10, R11 – сопротивления выбираются в зависимости от желаемых

параметров петли ФАПЧ; – управляющее напряжение;

VCO1 – генератор управляемый напряжением.

При подаче опорной частоты только на один из входов (REFSQ или REFSIN) незадействованный вход должен быть подключен к шине общий через конденсатор емкостью 10 пФ.

Допускается подача опорной частоты на оба входа одновременно. Выбор входа подачи опорной частоты см. п. 5.2 «Тракт делителя опорной частоты».

# Рисунок 12 – Типовая схема включения микросхемы с активным петлевым фильтром 4-го порядка

Микросхема может использоваться с активным и пассивным петлевым фильтром. Диапазон выходного напряжения ЗРБ ограничен напряжением питания микросхемы, поэтому при использовании пассивного фильтра этим же напряжением ограничен диапазон управляющего напряжения генератора управляемого (ГУН). Для расширения диапазона перестройки ГУН напряжением применяться активный петлевой фильтр на базе операционного усилителя (ОУ) с высоким напряжением питания. При этом на неинвертирующий вход ОУ должно быть подано опорное напряжение, близкое к половине напряжения питания ЗРБ. Активный фильтр включен по инвертирующей схеме. Для замыкания петли ФАПЧ необходимо изменить полярность фазового детектора, что производится установкой PFDSIGN = 1.

Uco

### 7 Предельно-допустимые характеристики микросхемы

Таблица 9 – Предельно-допустимые режимы эксплуатации и предельные электрические режимы микросхем

|                                                                                                                        | <u>a</u> <u>e</u>        |                                   | Норма параметра |                     |                      |  |

|------------------------------------------------------------------------------------------------------------------------|--------------------------|-----------------------------------|-----------------|---------------------|----------------------|--|

| Наименование параметра,<br>единица измерения                                                                           | Буквенное<br>обозначение | Предельно-<br>допустимый<br>режим |                 | Предельный<br>режим |                      |  |

|                                                                                                                        |                          | не<br>менее                       | не<br>более     | не<br>менее         | не<br>более          |  |

| Напряжение питания, В                                                                                                  | U <sub>CC</sub>          | 3,0                               | 3,6             | _                   | 4,0*<br>3,9          |  |

| Входное напряжение высокого уровня на<br>входах CLK, LE, DATA                                                          | U <sub>IH</sub>          | 2,0                               | Ucc             | -                   | U <sub>CC</sub> +0,3 |  |

| Входное напряжение низкого уровня на входах CLK, LE, DATA                                                              | UıL                      | 0                                 | 0,8             | - 0,3               | _                    |  |

| Выходной ток высокого уровня на выводе MUXOUT, мА                                                                      | I <sub>OH</sub>          | - 1                               | _               | _                   | _                    |  |

| Выходной ток низкого уровня на выводе MUXOUT, мА                                                                       | I <sub>OL</sub>          | _                                 | 1               | -                   | _                    |  |

| Входная мощность опорного сигнала синусоидальной формы, дБм                                                            | P <sub>SIN</sub>         | - 6                               | 12              | _                   | _                    |  |

| Емкость нагрузки на выводе MUXOUT, пФ                                                                                  | C <sub>L</sub>           | _                                 | 10              | _                   | _                    |  |

| Размах опорного сигнала прямоугольной формы, В                                                                         | U <sub>SQ</sub>          | 1,5                               | Ucc             | _                   | U <sub>CC</sub> +0,3 |  |

| Частота основного сигнала, ГГц:  – при мощности сигнала не менее минус 3,5 дБм;  – при мощности сигнала не менее 4 дБм | f                        | 0,4<br>0,1                        | 12<br>12        | _                   | -                    |  |

| Частота опорного сигнала, МГц:  – для сигнала синусоидальной формы;  – для сигнала прямоугольной формы                 | f <sub>REF</sub>         | 20                                | 250<br>250      | _                   | _                    |  |

| Частота сравнения фазового детектора, МГц:  – в дробном режиме;  – в целочисленном режиме                              | f <sub>PFD</sub>         | _                                 | 70<br>150       | _                   | -                    |  |

| Тактовая частота интерфейса программирования на входе СLK, МГц                                                         | f <sub>CLK</sub>         | _                                 | 10              | _                   | _                    |  |

| Входная мощность основного сигнала, дБм – при частоте сигнала не менее 100 МГц; – при частоте сигнала не менее 400 МГц | Р                        | 4 - 3,5                           | 10<br>10        | _                   | -                    |  |

<sup>\*</sup> Длительность воздействия предельного режима не более 24 часов

Примечание — Не допускается одновременное воздействие двух и более предельных режимов

#### 8 Электрические параметры микросхемы

Таблица 10 – Электрические параметры микросхемы

| Наименование параметра,<br>единица измерения,                                     | Буквенное<br>обозначение<br>параметра | Норма<br>параметра |             | Температура<br>среды, °С |

|-----------------------------------------------------------------------------------|---------------------------------------|--------------------|-------------|--------------------------|

| режим измерения                                                                   | Букв<br>обозн<br>пара                 | не<br>менее        | не<br>более | Темпе                    |

| Выходное напряжение высокого уровня на выводе MUXOUT, В                           | U <sub>OH</sub>                       | 2,8                | _           |                          |

| Выходное напряжение низкого уровня на выводе MUXOUT, В                            | Uol                                   | _                  | 0,1         |                          |

| Динамический ток потребления, мА                                                  | locc                                  | _                  | 130         |                          |

| Ток потребления в состоянии пониженного энергопотребления, мкА                    | I <sub>CCS</sub>                      | _                  | 50          |                          |

| Ток утечки высокого уровня на цифровых входах CLK, DATA, LE, мкА                  | I <sub>ILH</sub>                      | - 1,0              | 1,0         |                          |

| Ток утечки низкого уровня на цифровых входах<br>CLK, DATA, LE, мкА                | I <sub>ILL</sub>                      | - 1,0              | 1,0         |                          |

| Ток утечки на выходе СР, мкА                                                      | I <sub>LD</sub>                       | - 1,0              | 1,0         | 25,                      |

| Максимальный выходной втекающий ток зарядноразрядного блока на выводе СР, мА      | I <sub>CP</sub> SI MAX                | 3,6                | 4,4         | 125,<br>- 60             |

| Минимальный выходной втекающий ток зарядноразрядного блока на выводе СР, мкА      | I <sub>CP</sub> SI MIN                | 114                | 136         |                          |

| Максимальный выходной вытекающий ток зарядноразрядного блока на выводе СР, мА     | I <sub>CP</sub> SO MAX                | - 4,4              | - 3,6       |                          |

| Минимальный выходной вытекающий ток зарядноразрядного блока на выводе СР, мкА     | I <sub>CP SO MIN</sub>                | - 136              | - 114       |                          |

| Коэффициент деления опорной частоты, 1                                            | DREF                                  | 1                  | 16383       |                          |

| Целая часть коэффициента деления основной                                         |                                       | 24                 | 131067      |                          |

| частоты прескалера, 1:  – для режима прескалера 4/5;  – для режима прескалера 8/9 | INT                                   | 56                 | 262143      |                          |

Примечание — Режимы измерения параметров приведены в технических условиях АЕНВ.431230.245ТУ в таблице норм и режимов электрических параметров микросхем при испытаниях

Таблица 11 – Электрические параметры микросхем, измеряемые на пластине (при бескорпусной поставке)

| Наименование параметра,                                           | зенное<br>начение<br>аметра          | Норма<br>параметра |             | оатура<br>ы, °С          |  |

|-------------------------------------------------------------------|--------------------------------------|--------------------|-------------|--------------------------|--|

| единица измерения,<br>режим измерения                             | Буквенное<br>обозначени<br>параметра | не<br>менее        | не<br>более | Температура<br>среды, °С |  |

| Выходное напряжение высокого уровня на выводе MUXOUT, В           | U <sub>OH</sub>                      | 2,8                | _           | 25                       |  |

| Выходное напряжение низкого уровня на выводе MUXOUT, В            | U <sub>OL</sub>                      | I                  | 0,1         | 25                       |  |

| Ток потребления в состоянии пониженного<br>энергопотребления, мкА | Iccs                                 | _                  | 50          | 25                       |  |

| Ток утечки высокого уровня на цифровых входах CLK, DATA, LE, мкА  | I <sub>ILH</sub>                     | -1                 | 1           | 25                       |  |

| Ток утечки низкого уровня на цифровых входах CLK, DATA, LE, мкА   | I <sub>ILL</sub>                     | -1                 | 1           | 25                       |  |

| Функциональный контроль                                           | ФК                                   | _                  | _           | 25                       |  |

# 9 Справочные данные

Таблица 12 – Справочные параметры микросхемы

| Наименование параметра,                                                                                                                                                                                                          | нное<br>чение<br>четра               | Норма<br>параметра |             | атура<br>ды<br>са), °С         |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|--------------------|-------------|--------------------------------|--|

| единица измерения,<br>режим измерения                                                                                                                                                                                            | Буквенное<br>обозначени<br>параметра | не<br>менее        | не<br>более | Температ<br>средь<br>(корпуса) |  |

| Пороговое напряжение включения, В                                                                                                                                                                                                | $U_{POR\_H}$                         | _                  | 2           | 25                             |  |

| Пороговое напряжение выключения, В                                                                                                                                                                                               | $U_{POR\_L}$                         | 1                  | _           | 25                             |  |

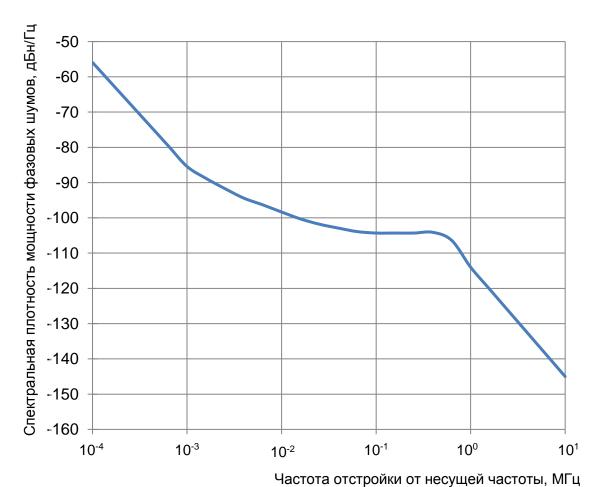

| Нормированный уровень тепловых фазовых шумов в целочисленном режиме, дБн/Гц (измеряется на отстройке от несущей частоты 200 кГц), при f = 12 ГГц, f <sub>PFD</sub> = 100 МГц, Ucc = 3,3 B, ICP = <11111>                         | $P_{n\_floor}$                       | _                  | -227        | 25                             |  |

| Нормированный уровень фликкер фазовых шумов в целочисленном режиме, дБн/Гц (измеряется на отстройке от несущей частоты 10 кГц, нормируется на частоту 1 ГГц), f = 12 ГГц, f <sub>PFD</sub> = 100 МГц, Ucc = 3,3 B, ICP = <11111> | $P_{n\_flick}$                       | -                  | -118        | 25                             |  |

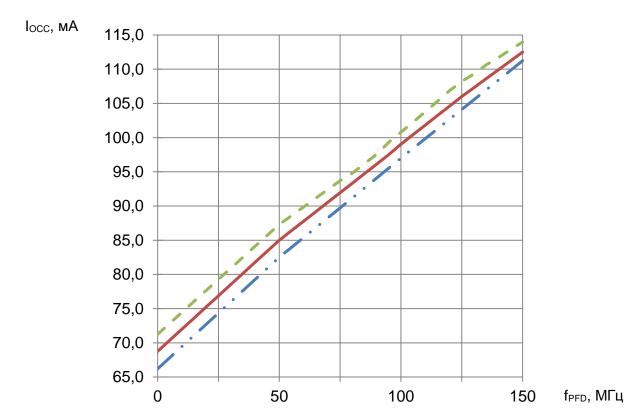

Рисунок 13 – Зависимость динамического тока потребления locc от частоты сравнения фазового детектора fpfd в целочисленном режиме, при Ucc = 3,3 В

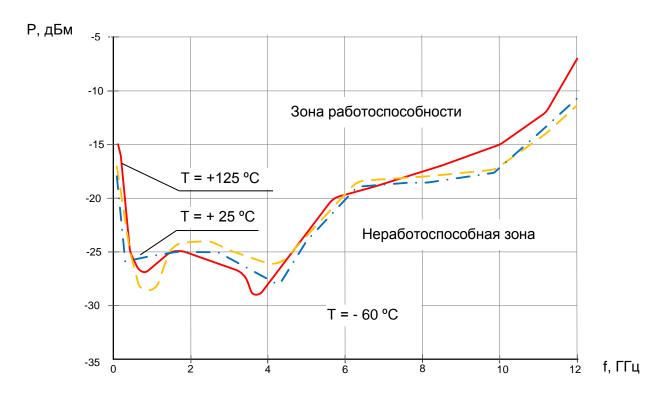

Рисунок 14 – Зависимость минимального значения мощности Р основного сигнала по входу от основной частоты f (чувствительность), при Ucc = 3,3 В

Рисунок 15 – Зависимость спектральной плотности мощности фазовых шумов от частоты отстройки от несущей частоты в целочисленном режиме на основной частоте f = 12 ГГц, при REG4<4:0> = <11111>, fPFD = 100 МГц,

Ucc = 3,3 B, T = 25 °C

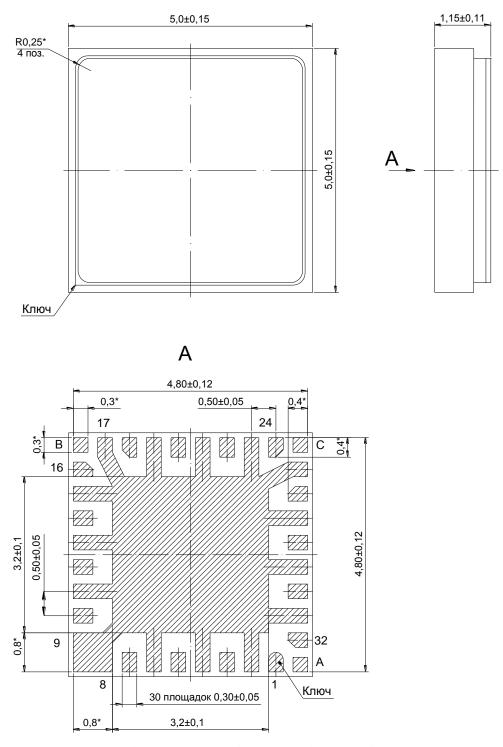

## 11 Габаритный чертеж микросхемы

Рисунок 16 - Корпус 5102.32-2К

- 1 Размеры контактных площадок (КП) кристалла

- 1 3, 12 9, 27 29: (105 x 90) мкм,

- 4 11, 20 26: (90 x 105) мкм.

- Материал КП AI (алюминий).

- 2 Толщина кристалла (0,305 ± 0,015) мм.

- 3 М маркировка кристалла MLDR89 показана условно.

- 4 Координаты КП см. таблицу 11.

Рисунок 17 – Кристалл (бескорпусное исполнение)

Таблица 13 – Координаты КП кристалла

| № КП   | Обозначение | Коордиі | наты КП | № КП    | Обозначение | Коорди  | наты КП |

|--------|-------------|---------|---------|---------|-------------|---------|---------|

| Mº KII | КΠ          | Х       | Υ       | IN WILL | ΚП          | Х       | Υ       |

| 1      | GND         | -761,50 | -201,00 | 16      | GND         | 761,50  | 71,00   |

| 2      | LE          | -761,50 | -331,00 | 17      | CP          | 761,50  | 201,00  |

| 3      | DATA        | -761,50 | -461,00 | 18      | GND         | 761,50  | 331,00  |

| 4      | CLK         | -461,00 | -761,50 | 19      | GND         | 761,50  | 461,00  |

| 5      | GND         | -331,00 | -761,50 | 20      | VCCA3       | 450,98  | 761,50  |

| 6      | MUXOUT      | -201,00 | -761,50 | 21      | Rref        | 320,98  | 761,50  |

| 7      | GND         | -71,00  | -761,50 | 22      | GND         | 190,98  | 761,50  |

| 8      | VCC         | 59,00   | -761,50 | 23      | VCCA4       | -71,00  | 761,50  |

| 9      | GND         | 201,00  | -761,50 | 24      | REFSQ       | -201,00 | 761,50  |

| 10     | VCCA1       | 331,00  | -761,50 | 25      | GND         | -331,00 | 761,50  |

| 11     | VCCA1       | 461,00  | -761,50 | 26      | SINVDD      | -461,00 | 761,50  |

| 12     | RFIN        | 761,50  | -461,00 | 27      | GND         | -761,50 | 461,00  |

| 13     | GND         | 761,50  | -331,0  | 28      | REFSIN      | -761,50 | 331,00  |

| 14     | GND         | 761,50  | -201,00 | 29      | SINCAP      | -761,50 | 201,00  |

| 15     | VCCA2       | 761,50  | -59,00  |         |             |         |         |

#### 12 Информация для заказа

| Обозначение<br>микросхемы | Маркировка | Тип корпуса | Температурный<br>диапазон |

|---------------------------|------------|-------------|---------------------------|

| 1508AC015                 | 8AC1       | 5102.32-2K  | минус 60 – 125 °C         |

| K1508AC015                | K8AC1      | 5102.32-2K  | минус 60 – 125 °C         |

| K1508AC015K               | K8AC1•     | 5102.32-2K  | 0 – 70°C                  |

Микросхемы с приемкой «ВП» маркируются ромбом. Микросхемы с приемкой «ОТК» маркируются буквой «К».

Пример обозначения микросхем при заказе (в договоре на поставку) микросхем предназначенных:

- для ручной сборки (монтажа) аппаратуры:

микросхема 1508AC015 AEHB.431230.245ТУ;

- для автоматизированной сборки (монтажа) аппаратуры:

микросхема 1508AC015 AEHB.431230.245TУ, А.

Примечание — Микросхемы в бескорпусном исполнении поставляются в виде отдельных кристаллов, получаемых разделением пластины. Микросхемы поставляются в таре (кейсах) без потери ориентации. Маркировка микросхемы в бескорпусном исполнении — 1508AC01H4, K1508AC01H4 — наносится на тару.

# 13 Лист регистрации изменений

| <b>№</b><br>п/п | Дата       | Версия | Краткое содержание изменения                              | №№<br>изменяемых<br>листов |

|-----------------|------------|--------|-----------------------------------------------------------|----------------------------|

| 1               | 25.12.2015 | 1.0.0  | Введена впервые                                           |                            |

| 2               | 29.12.2016 | 2.0.0  | Приведение в соответствие с ТУ и КД лит. А                | По тексту                  |

| 3               | 05.04.2017 | 2.1.0  | Дополнения в разделе Описание функционирования микросхемы | 7, 13                      |

| 4               | 19.12.2017 | 2.2.0  | Исправлено значение параметра f <sub>REF</sub>            | 24                         |

|                 |            |        |                                                           |                            |

|                 |            |        |                                                           |                            |

|                 |            |        |                                                           |                            |

|                 |            |        |                                                           |                            |

|                 |            |        |                                                           |                            |

|                 |            |        |                                                           |                            |

|                 |            |        |                                                           |                            |

|                 |            |        |                                                           |                            |

|                 |            |        |                                                           |                            |

|                 |            |        |                                                           |                            |