# МИКРОСХЕМЫ ИНТЕГРАЛЬНЫЕ 1874ВЕ76Т, 1874ВЕ06Т, 1874ВЕ05Т

Руководство пользователя

## Содержание

| Введение                                                           | 8  |

|--------------------------------------------------------------------|----|

| 1 Назначение и область применения                                  | 9  |

| 2 Краткое техническое описание ИМС 1874ВЕ76Т, 1874ВЕ06Т, 1874ВЕ05Т | 10 |

| 2.1 Функциональные параметры:                                      | 10 |

| 2.2 Электрические параметры микросхем                              |    |

| 3 Архитектура изделий                                              |    |

| 3.1 Особенности архитектуры                                        | 24 |

| 3.2 Краткое описание функционирования микросхем комплекта          |    |

| 3.2.1 Процессорное ядро                                            |    |

| 3.2.2 Способы адресации                                            |    |

| 3.2.3 Прерывания                                                   |    |

| 3.2.4 Периферийные устройства                                      |    |

| 3.2.5 Синхронизация                                                |    |

| 4 Типы данных и адресация                                          |    |

| 4.1 Типы операндов                                                 | 20 |

| 4.2 Режимы адресации                                               |    |

| 4.2.3 Косвенная адресация с автоинкрементом                        |    |

| 4.2.4 Непосредственная адресация                                   |    |

| 4.2.5 Короткая Индексная адресация                                 |    |

| 4.2.6 Длинная Индексная адресация                                  |    |

| 4.2.7 Адресация с использованием Нулевого Регистра                 |    |

| 4.2.8 Адресация с использованием Указателя Стека                   |    |

| 4.3 Выборы способов адресации на языке ассемблера                  |    |

| 4.3.1 Прямая адресация                                             |    |

| 4.3.2 Индексная адресация                                          | 34 |

| 4.4 Стандарты и соглашения программного обеспечения                | 35 |

| 4.4.1 Использование регистров                                      |    |

| 4.4.2 Адресация 32-битных операндов                                |    |

| 4.4.3 Соединение подпроцедур                                       |    |

| 4.5 Защита и руководящие принципы программного обеспечения         | 36 |

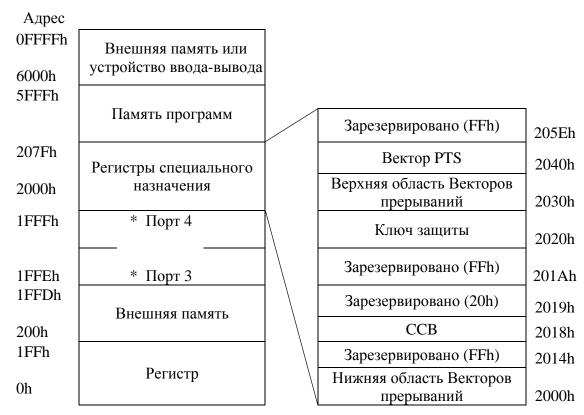

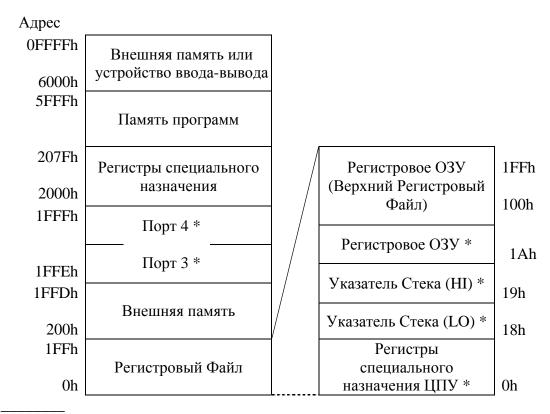

| 5 Распределение памяти                                             | 37 |

| 5.1 Разделы внешней памяти                                         | 38 |

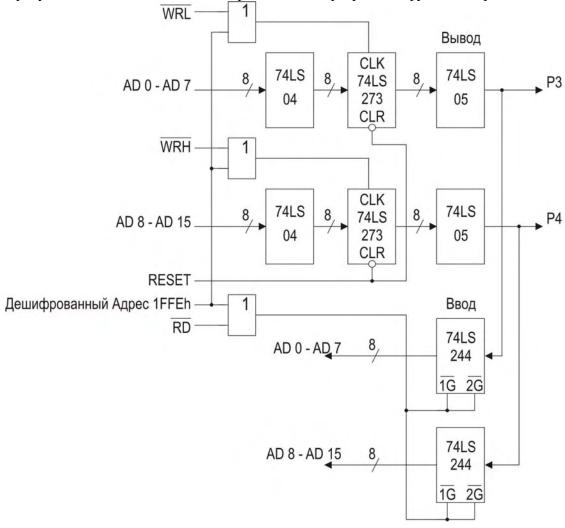

| 5.2 Порты 3 и 4                                                    |    |

| 5.3 Программная память и память специального назначения            |    |

| 5.3.1 Выбор внутренней или внешней памяти                          |    |

| 5.3.2 Программная память                                           | 38 |

| 5.3.3 Память специального назначения                               | 38 |

| 5.4 Регистровый файл                                               | 40 |

| 5.4.1 Регистровое ОЗУ общего назначения                            |    |

| 5.4.2 Указатель стека (SP)                                         |    |

| 5.4.3 Регистры специальных функций (SFRs)                          |    |

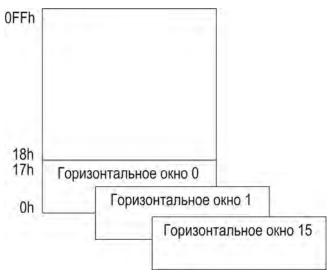

| 5.5 Создание горизонтальных окон                                   |    |

| 5.5.1 Выбор горизонтального окна                                   |    |

| 5.5.2 Горизонтальное окно 0 (HWindow 0)                            |    |

| 5.5.3 Горизонтальное окно 1 (HWindow 1)                            | 43 |

| 5.5.4 Горизонтальное окно 15 (HWindow 15)                            | 43 |

|----------------------------------------------------------------------|----|

| 5.6 Создание вертикальных окон                                       | 44 |

| 5.6.1 Выбор вертикального окна                                       | 45 |

| 5.6.2 Создание вертикальных окон и способы адресации                 | 45 |

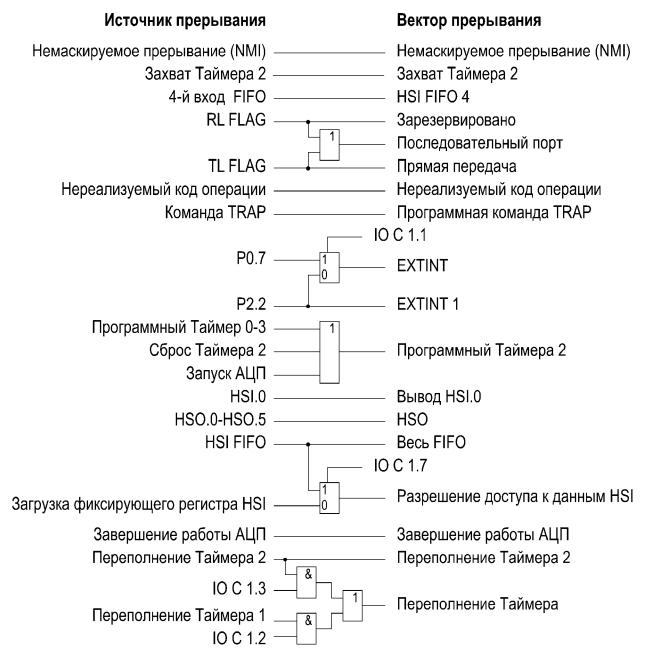

| 6 Прерывания                                                         | 46 |

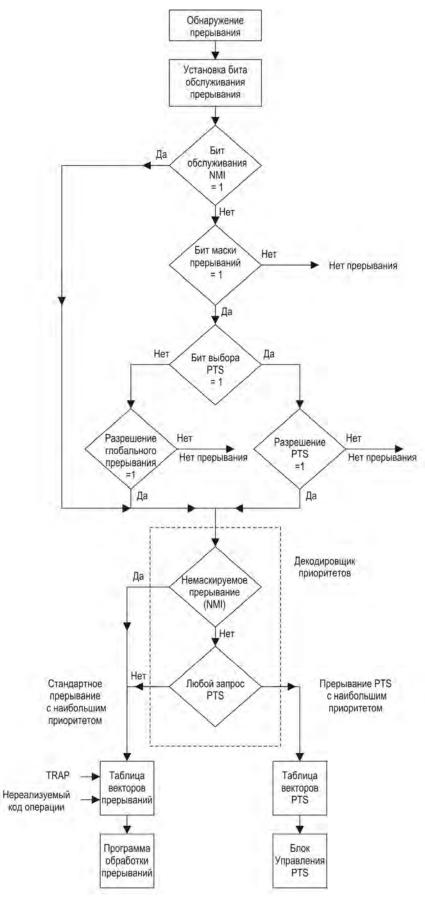

| 6.1 Обработка прерываний                                             |    |

| 6.1.1 Контроллер прерываний                                          |    |

| 6.1.2 Периферийный Сервер (PTS)                                      | 46 |

| 6.2 Приоритеты прерываний                                            | 48 |

| 6.2.1 Модификация приоритетов прерываний                             | 48 |

| 6.3 Синхронизация прерываний                                         | 51 |

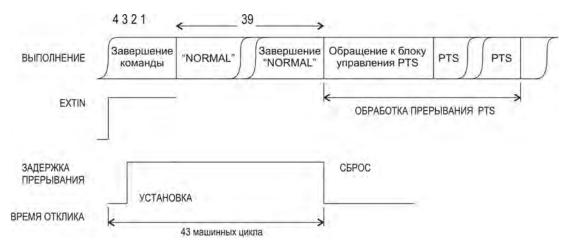

| 6.3.1 Время ожидания прерываний                                      | 51 |

| 6.3.2 Вычисление времени ожидания                                    | 52 |

| 6.4 Специальные прерывания                                           | 53 |

| 6.4.1 Неподдерживаемые Коды                                          | 53 |

| 6.4.2 Программное прерывание                                         | 53 |

| 6.4.3 Немаскируемое прерывание (NMI)                                 | 53 |

| 6.5 Программирование прерываний                                      | 54 |

| 6.5.1 Выбор способа обработки прерываний: через PTS или стандартного | 54 |

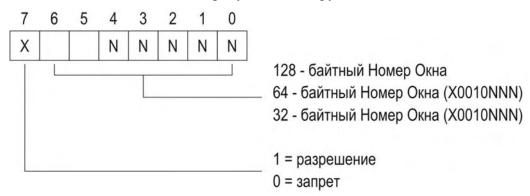

| 6.5.2 Разрешение РТS прерываний                                      |    |

| 6.5.3 Выбор источников прерываний                                    | 55 |

| 6.5.4 Регистры масок прерываний                                      | 56 |

| 6.5.5 Регистры ожидания прерываний                                   |    |

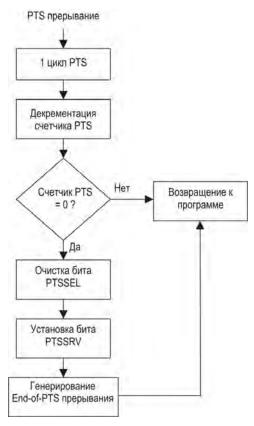

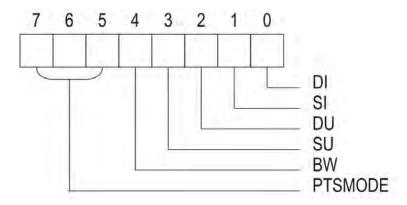

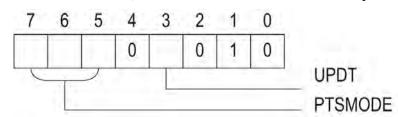

| 6.6 Блоки управления PTS                                             |    |

| 6.6.1 Регистр PTSCOUNT                                               | 58 |

| 6.6.2 Регистр PTSCON                                                 |    |

| 6.7 Режим одиночной передачи                                         |    |

| 6.7.1 Пример режима одиночной передачи                               |    |

| 6.8 Режим блочной передачи                                           |    |

| 6.8.1 Пример режима блочной передачи                                 |    |

| 6.9 Режим сканирования АЦП                                           |    |

| 6.9.1 PTS циклы в режиме сканирования АЦП                            |    |

| 6.9.2 Режим сканирования АЦП. Пример 1                               |    |

| 6.9.3 Режим сканирования АЦП. Пример 2                               |    |

| 6.10 Режим HSI                                                       |    |

| 6.10.1 Пример режима HSI                                             |    |

| 6.11 Режим HSO                                                       |    |

| 6.11.1 Пример режима HSO                                             |    |

| 7 Порты ввода-вывода                                                 |    |

| 7.1 Обзор функциональных возможностей                                | 66 |

| 7.1.1 Входной вывод порта                                            |    |

| 7.1.2 Выходной вывод порта                                           |    |

| 7.1.3 Квазидвунаправленный вывод порта                               |    |

| 7.1.4 Двунаправленный вывод порта с открытым стоком                  |    |

| 7.2 Программирование портов І/О                                      |    |

| 7.2.1 Входной порт                                                   |    |

| 7.2.2 Порт вывода                                                    |    |

| 7.2.3 Доступ к портам 3 и 4                                          |    |

| 7.3 Аппаратное подключение к квазидвунаправленным портам             |    |

| 8 Последовательный порт ввода-вывода                                    | 77   |

|-------------------------------------------------------------------------|------|

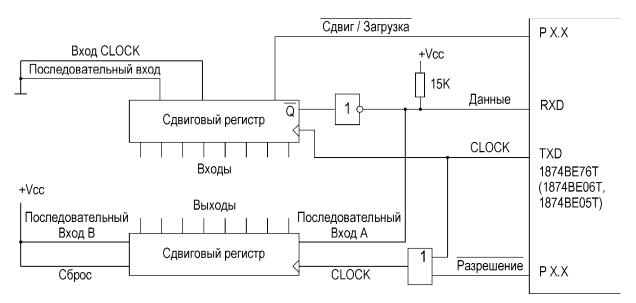

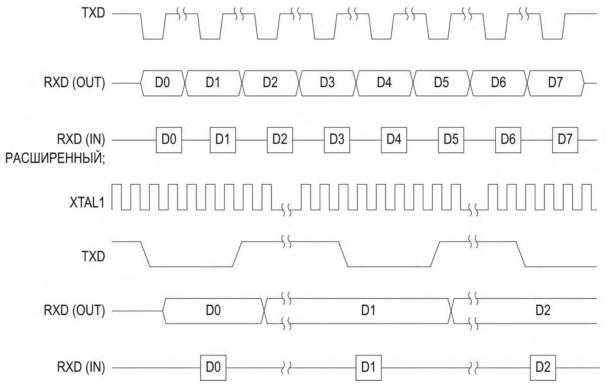

| 8.1 Режим 0 (МОДЕ 0)                                                    | 77   |

| 8.2 Асинхронные режимы                                                  |      |

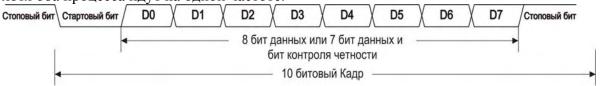

| 8.2.1 Режим 1                                                           | 79   |

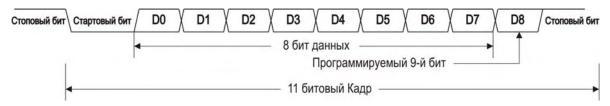

| 8.2.2 Режим 2                                                           | 79   |

| 8.2.3 Режим 3                                                           |      |

| 8.2.4 Временные соотношения в Режимах 2 и 3                             |      |

| 8.2.5 Мультипроцессорные связи                                          |      |

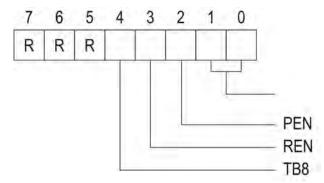

| 8.3 Программирование последовательного порта                            |      |

| 8.3.1 Выбор режима связи и разрешение проверки чётности                 |      |

| 8.3.2 Конфигурирование TXD и RXD                                        |      |

| 8.3.3 Разрешение работы по прерываниям для последовательного порта      |      |

| 8.3.4 Программирование скорости обмена и источника синхронизации        |      |

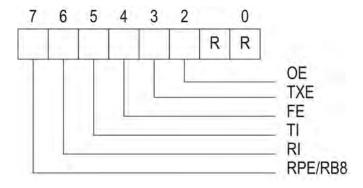

| 8.4 Состояние последовательного порта                                   | 84   |

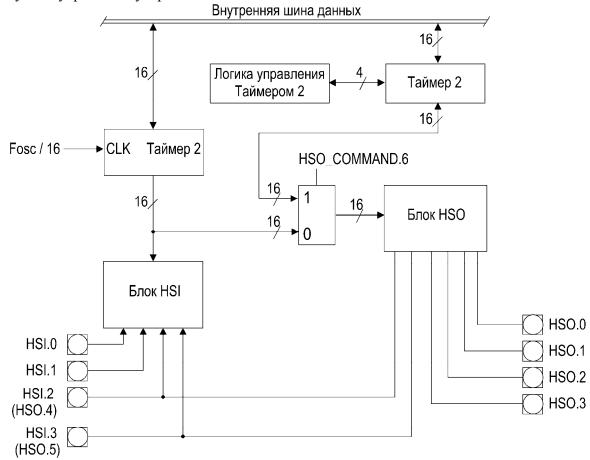

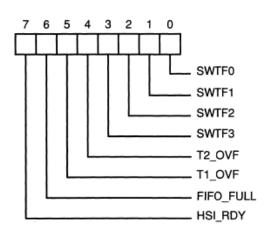

| 9 Устройство высокоскоростного ввода-вывода                             | 86   |

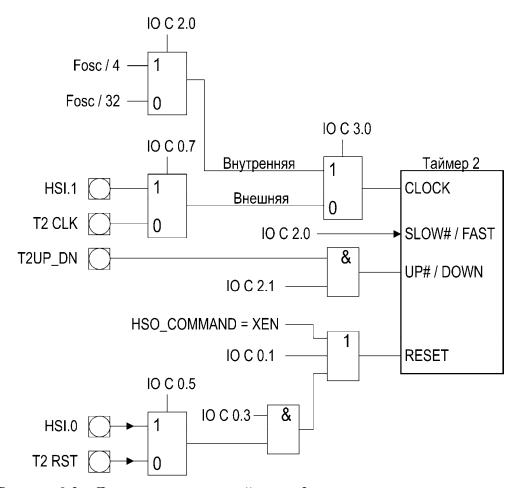

| 9.1 Таймеры                                                             | 86   |

| 9.1.1 Функции таймера 1                                                 |      |

| 9.1.2 Функции таймера 2                                                 |      |

| 9.1.3. Программирование Модуля таймера 2                                |      |

| 9.1.4 Использование Внешних Входов таймера 2                            |      |

| 9.1.5 Прерывания таймера                                                |      |

| 9.1.6 Предосторожности при работе с таймером                            |      |

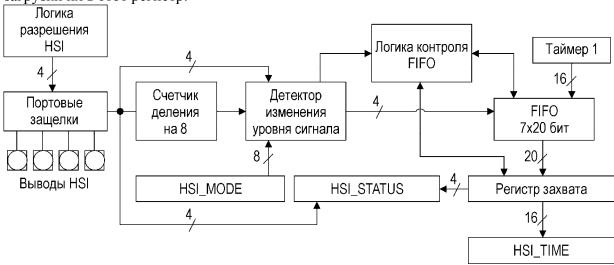

| 9.2 Модуль высокоскоростного ввода HSI                                  |      |

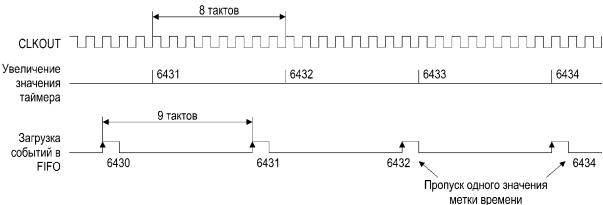

| 9.2.1 Временные Соотношения для Событий в HSI                           |      |

| 9.2.2 Чтение Информации о Событии                                       | 94   |

| 9.2.3 Программирование HSI Модуля                                       | 94   |

| 9.3 Модуль высокоскоростного вывода HSO                                 | 98   |

| 9.3.1 Функционирование HSO                                              | 98   |

| 9.3.2 Программирование HSO Модуля                                       | 99   |

| 9.3.3 Использование модуля HSO как широтно-импульсного модулятора (PWM) |      |

| 9.3.4 Синхронизация Выхода HSO.                                         | .104 |

| 10 Аналого-цифровой преобразователь                                     | .105 |

| 10.1 Обзор функций АЦП                                                  | 105  |

| 10.2 Программирование АЦП                                               | 106  |

| 10.2.1 Выбор времени запоминания и преобразования                       |      |

| 10.2.2 Программирование ІОС2 Регистра                                   |      |

| 10.2.3 Программирование регистра ADCOMMAND                              |      |

| 10.3 Чтение результатов преобразования                                  |      |

| 10.4 Интерфейс с АЦ-преобразователем                                    |      |

| 10.4.1 Аналоговая земля и источник опорного напряжения                  |      |

| 10.4.2 Совместное использование аналоговых и цифровых входов            |      |

| 10.5 Передаточная функция и источник ошибок АЦП                         |      |

| 11 Широтно-импульсный модулятор (PWM)                                   | 115  |

| 11.1 Функциональный обзор PWM                                           | 115  |

| 11.2. Программирование рабочего цикла PWM                               |      |

| 11.3 Разрешение выходов PWM          | 1. | 1 | 7 |

|--------------------------------------|----|---|---|

| 11.4 Формирование аналоговых выходов | 1. | 1 | 7 |

| 12 Специальные режимы работы                                       | ••••• |

|--------------------------------------------------------------------|-------|

| 12.1 Режим IDLE                                                    |       |

| 12.1.1 Вход в IDLE Режим                                           |       |

| 12.1.2 Выход из IDLE Режим                                         |       |

| 12.2 Режим POWERDOWN                                               |       |

| 12.2.1 Запрещение Режима POWERDOWN                                 |       |

| 12.2.2 Переход в Режим POWERDOWN                                   |       |

| 12.2.3 Выход из Режима POWERDOWN                                   |       |

| 12.3 Вход в режимы, зарезервированные для тестирования             |       |

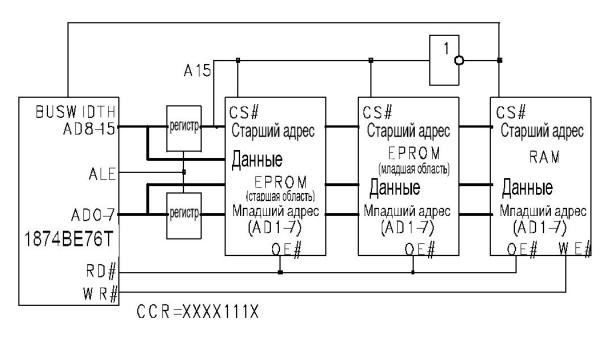

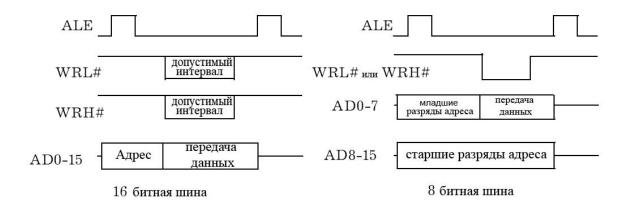

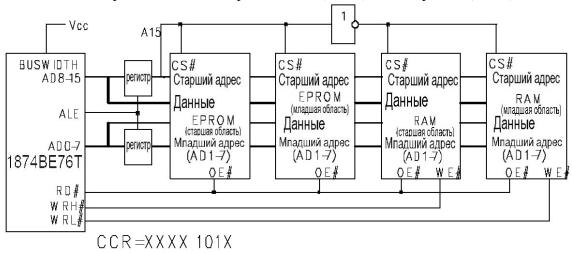

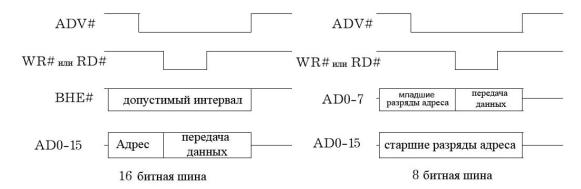

| 13 Интерфейс внешней памяти                                        |       |

| 13.1 Сигналы интерфейса внешней памяти                             |       |

| 13.2 Регистр конфигурации кристалла                                |       |

|                                                                    |       |

| 13.3 Разрядность шины и конфигурация памяти                        |       |

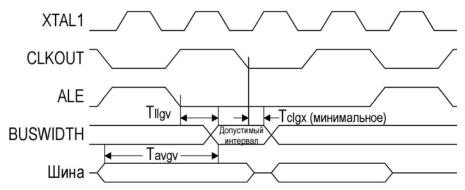

| 13.3.1 Временные требования для сигнала BW                         |       |

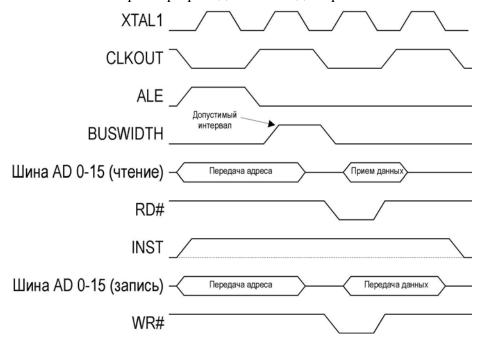

| 13.3.2 Шина разрядностью 16 бит                                    |       |

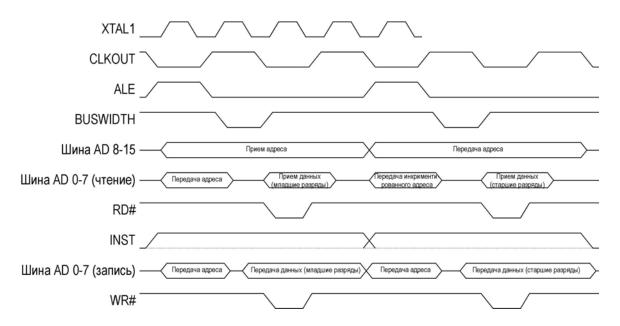

| 13.3.3 Шина Разрядностью 8 Бит                                     |       |

| 13.4 Управление сигналом READY                                     |       |

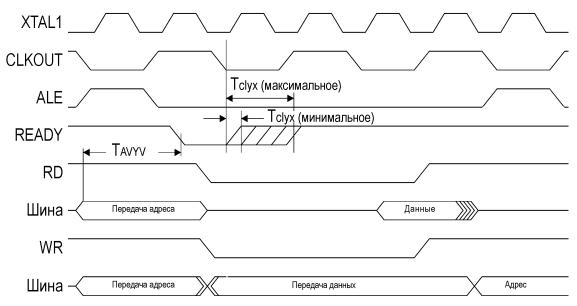

| 13.4.1 Временные Требования для Сигнала READY                      |       |

| 13.5 Протокол захвата шины                                         |       |

| 13.5.1 Разрешение Протокола Захвата Шины                           |       |

| 13.5.2 Запрещение Протокола Захвата Шины                           |       |

| 13.5.3 Скрытое состояние HOLD (Hold Latency)                       |       |

| 13.5.4 Возврат Управления Шины                                     |       |

| 13.6 Режимы управления шиной                                       |       |

| 13.6.1 Стандартный режим управления шиной (Standart Bus - Control) |       |

| 13.6.2 Режим Write Strobe Mode                                     |       |

| 13.6.3 Режим Address Valid Strobe                                  |       |

| 13.6.4 Режим Address Valid with Write Strobe                       |       |

| 13.7 Временные соотношения системной шины                          |       |

| 13.7.1 Перечень Принятых Сокращений                                | ••••  |

| 14 Программирование постоянной памяти                              | ••••• |

| 14.1 Общее описание                                                |       |

| 14.2 Режимы программирования                                       |       |

| 14.2.1 Выбор режима программирования                               |       |

| 14.3 Функции выводов в режиме программирования                     |       |

| 14.4 Распределение памяти                                          |       |

| 14.5 Включение и выключение питания                                |       |

| 14.5.1 Последовательность включения питания                        |       |

| 14.5.2 Последовательность выключения питания                       |       |

| 14.5.2 последовательность выключения питания                       |       |

| 14.6.1 Биты кода защиты в ССR                                      |       |

| 14.6.2 Биты кода защиты в ССК                                      |       |

| 14.6.3 Ключ защиты                                                 |       |

|                                                                    |       |

| 14.7 Модифицированный быстрый (QUICK_PULSE) алгоритм               |       |

| 14.8 Слово-сигнатура                                               |       |

| 14.9 Режим программирования AUTO                                   |       |

| 14.10 Режим программирования SLAVE                                 | ••••• |

| L/L III L Pengam SL A V H                                          |       |

| 14.10.3 Алгоритм режима SLAVE                                            | 157        |

|--------------------------------------------------------------------------|------------|

| 14.10.4 Команды Program Word и Dump Word                                 |            |

| 14.11 Режим ввода содержимого памяти (ROM-DUMP)                          | 162        |

| 14.12 Режим RUN-TIME                                                     | 162        |

| 15 Рекомендации по отладочным средствам ИМС                              | 163        |

| 15.1 Программаторы для программируемого варианта ИМС                     | 163        |

| 15.2 Описание инструментальных средств для ИМС                           | 163        |

| 15.3 Интегрированный пакет разработки и отладки систем на базе микроконт | гроллеров. |

| (PROJECT-96)                                                             | 163        |

| 15.3.1 Внутрисхемный эмулятор РІСЕ-196                                   | 163        |

| 15.4 Отладчик-симулятор микроконтроллеров семейства MCS-196 PDS-96       | 165        |

| 15.5 Кросс-макроассемблер МСА-96                                         | 166        |

| 15.6 Кросс-компилятор языка Си МСС-96                                    | 167        |

| 16 Заключение                                                            | 168        |

| Приложение А (обязательное)                                              |            |

| Система команд МК 1874BE76T (1874BE06T, 1874BE05T)                       | 169        |

| Приложение Б (обязательное) Описание сигналов                            | 208        |

| Приложение В (рекомендованное) Регистры                                  | 225        |

| Іист регистрации изменений                                               | 274        |

#### Введение

В настоящем руководстве КФДЛ.431295.019 приведено описание архитектуры, функционального построения, системы команд И особенностей применения микросхем 1874BE76T, 1874BE06T И 1874BE05T. Первые две микросхемы представляют собой СБИС однокристальных 16-разрядных микроконтроллеров с тактовой частотой 20 МГц, ОЗУ (488×8) бит, 8-канальным 10-разрядным АЦП, 3-канальным ШИМ и последовательным портом ввода-вывода, в том числе с внутренней памятью программ типа ОТР EPROM (для ИМС 1874ВЕ76Т) объемом (16К×8) бит (функциональные аналоги TN87C196KC-20, TN80C196KC-20 фирмы Intel). Микросхема представляет собой стойкий 1874BE05T К специальным воздействующих факторов вариант микроконтроллера 1874ВЕ06Т без АЦП.

Изделие 1874ВЕ05Т послужит цели развития отечественной элементной базы для применения в различных системах управления и радиосвязи.

Настоящее руководство может служить практическим пособием по применению микроконтроллеров для разработчиков систем на основе ИМС 1874BE76T, 1874BE06T и 1874BE05T.

#### 1 Назначение и область применения

Архитектура микроконтроллеров ориентирована для создания управляющих систем, функционирующих в режиме реального времени с возможностью адаптации и модификации под конкретные приложения. Изделия могут служить элементной базой для систем управления различной аппаратурой, в том числе силовой электроникой, автомобильной техникой и т. д.

Наличие средств инструментальной отладки обеспечивает как эффективное проектирование систем на основе микроконтроллера, так и возможность смены алгоритма работы при создании модификаций систем.

Микросхемы представляют собой комплект высокопроизводительных 16-разрядных микроконтроллеров:

- 1874BE76T 16-разрядный микроконтроллер со встроенной памятью программ типа OTP EPROM (16К×8) бит (аналог TN87C196KC-20 фирмы Intel);

- 1874BE06T 16-разрядный микроконтроллер без встроенной памяти программ (функциональный аналог TN87C196KC-20 фирмы Intel), предназначенный для применения в системах встроенного управления;

- 1874BE05T стойкий к специальным видам внешних воздействующих факторов 16-разрядный микроконтроллер с системой команд микроконтроллера 1874BE36.

#### **2 Краткое техническое описание ИМС 1874ВЕ76Т, 1874ВЕ06Т, 1874ВЕ05Т**

#### 2.1 Функциональные параметры:

| - разрядность данных, бит                                    | 16;       |

|--------------------------------------------------------------|-----------|

| - тактовая частота, МГц                                      | 20;       |

| - динамически конфигурируемая шина данных, бит               | 8 или 16; |

| - встроенная память программ (однократно программируемая)    |           |

| типа OTP EPROM (только для микросхемы 1874BE76T. В           |           |

| микросхемах 1874ВЕ06Т и 1874ВЕ05Т отсутствует), бит          | 16K×8;    |

| - регистровое ОЗУ, бит                                       | 488×8;    |

| - адресуемая память, бит                                     | 64K×8;    |

| - число источников прерывания                                | 28;       |

| - число параллельных 8-разрядных портов ввода-вывода         | 5;        |

| - разрядность сторожевого таймера                            | 16;       |

| - число таймеров/счетчиков                                   | 2;        |

| - разрядность таймеров/счетчиков                             | 16;       |

| - универсальный последовательный порт                        | 1;        |

| - устройство высокоскоростного ввода-вывода                  | 4/6;      |

| - число разрядов 8-канального аналого-цифрового              |           |

| преобразователя (только для микросхем 1874ВЕ06Т и 1874ВЕ76Т, |           |

| в микросхеме 1874ВЕ05Т отсутствует)                          | 8, 10;    |

| - блок ШИМ сигналов                                          | 3;        |

| - периферийный сервер (PTS)                                  | 1.        |

Микросхемы выполнены в металлокерамическом планарном корпусе с четырехсторонним расположением выводов 4235.88-1 и предназначены для ручной и автоматической сборки в соответствии с ГОСТ РВ 20.39.412-97. Масса микросхемы не более 4,5 г.

Герметизация микросхем осуществляется шовной роликовой сваркой. Показатель герметичности корпуса по скорости утечки гелия не более  $5\times10^{-3}~\Pi a\cdot cm^3/c$ .

Микросхемы не имеют собственных резонансных частот ниже 100 Гц.

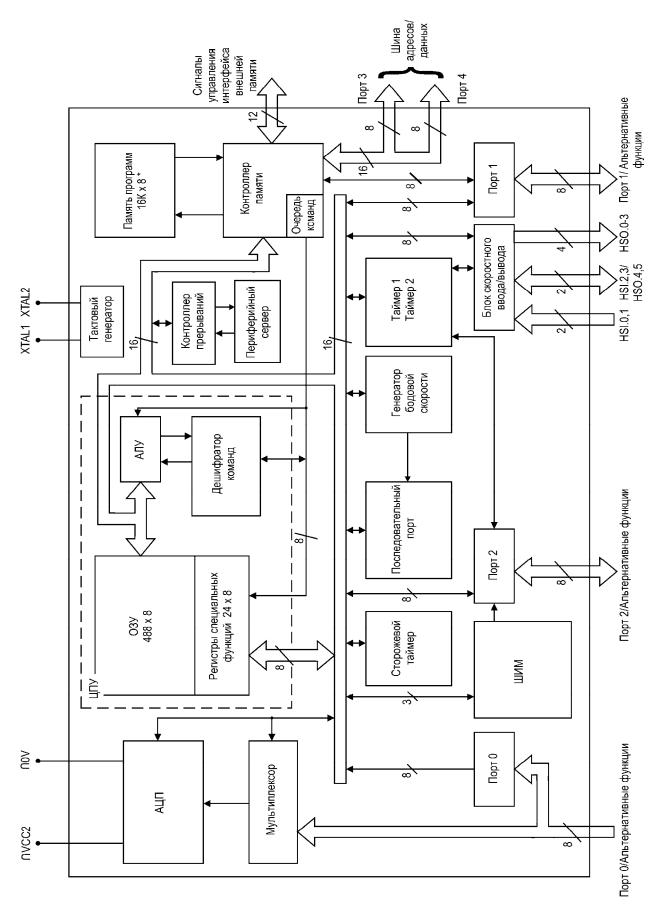

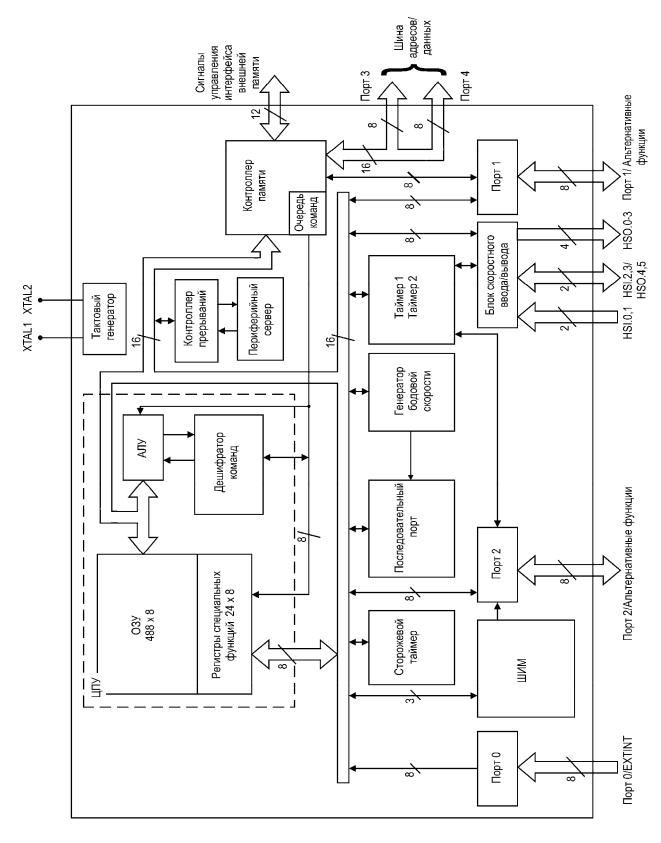

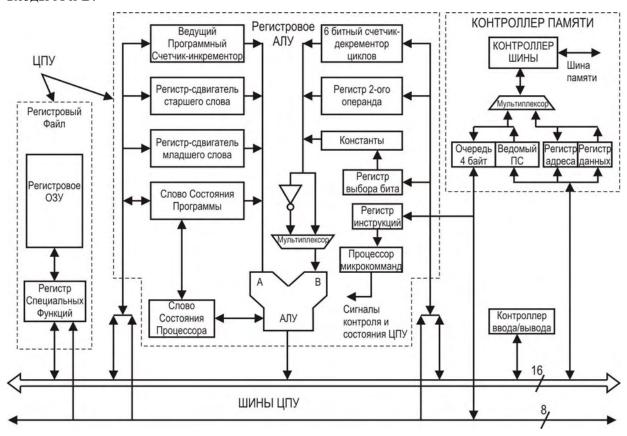

Структурная схема микросхем 1874BE76T, 1874BE06T приведена на рисунке 2.1. Структурная схема микросхемы 1874BE05T приведена на рисунке 2.2.

Рисунок 2.1 – Структурная схема микроконтроллеров 1874ВЕ76Т и 1874ВЕ06Т

<sup>\*</sup> Только для 1874ВЕ76Т (со встроенной памятью программ)

Рисунок 2.2 – Структурная схема микроконтроллера 1874ВЕ05Т

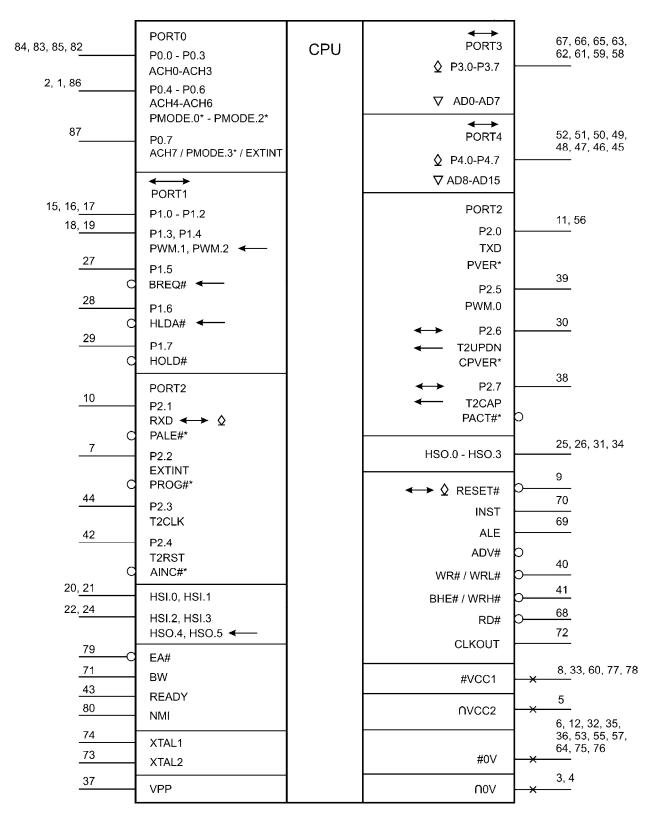

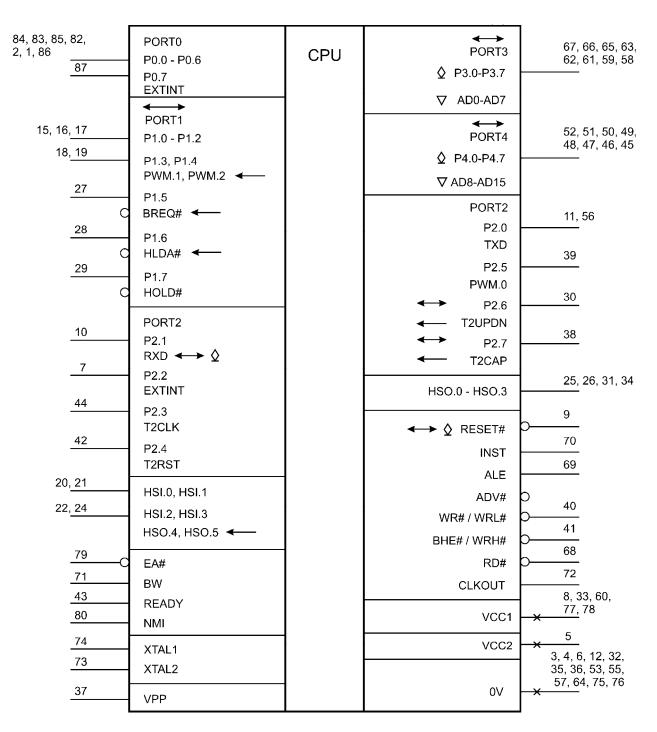

Условные графические обозначения микросхем приведены на рисунках 2.3 и 2.4. Функциональное назначение выводов микросхем приведено в таблице 2.1.

Рисунок 2.3 – Условное графическое изображение микросхем 1874BE76T, 1874BE06T

<sup>\*</sup> Только для микросхем 1874ВЕ76Т

Рисунок 3.2 – Условное графическое изображение микросхем 1874ВЕ05Т

| <u>Таблица 2.1 – 9</u> | Функцион | пальное назначение выводов микросхем                     |        | Γ           |

|------------------------|----------|----------------------------------------------------------|--------|-------------|

| 0.5                    | **       |                                                          | _      | Обозначение |

| Обозначение            | Номер    | Функциональное назначение                                | Тип    | альтернатив |

| вывода                 | вывода   | 1 9                                                      | вывода | ной функции |

| 1                      | 2        | 2                                                        | 4      | вывода      |

| 1                      | 2        | 3<br>Hzg savene avok 1974DE76T v 1974DE06T               | 4      | 5           |

| DO 0                   | 0.4      | Для микросхем 1874BE76T и 1874BE06T                      | т      | <u> </u>    |

| P0.0                   | 84       | Вход "порт 0, 0 разряд"                                  | I      | A CITO      |

| DO 1                   | 02       | Вход АЦП, канал 0                                        | I      | ACH0        |

| P0.1                   | 83       | Вход "порт 0, 1 разряд"                                  | I      | A CITA      |

| D0 0                   | 0.5      | Вход АЦП, канал 1                                        | I      | ACH1        |

| P0.2                   | 85       | Вход "порт 0, 2 разряд"                                  | I      | A CITO      |

| 70.0                   | 22       | Вход АЦП, канал 2                                        | I      | ACH2        |

| P0.3                   | 82       | Вход "порт 0, 3 разряд"                                  | I      |             |

|                        |          | Вход АЦП, канал 3                                        | I      | ACH3        |

| P0.4                   | 2        | Вход "порт 0, 4 разряд"                                  | I      |             |

|                        |          | Вход АЦП, канал 4                                        | I      | ACH4        |

|                        |          | Вход "режим программирования, 0 разряд"*                 | I      | PMODE.0*    |

| P0.5                   | 1        | Вход "порт 0, 5 разряд"                                  | I      |             |

|                        |          | Вход АЦП, канал 5                                        | I      | ACH5        |

|                        |          | Вход "режим программирования, 1 разряд"*                 | I      | PMODE.1*    |

| P0.6                   | 86       | Вход "порт 0, 6 разряд"                                  | I      |             |

|                        |          | Вход АЦП, канал 6                                        | I      | ACH6        |

|                        |          | Вход "режим программирования, 2 разряд"*                 | I      | PMODE.2*    |

| P0.7                   | 87       | Вход "порт 0, 7 разряд"                                  | I      |             |

|                        |          | Вход АЦП, канал 7                                        | I      | ACH7        |

|                        |          | Вход "режим программирования, 3 разряд"*                 | I      | PMODE.3*    |

|                        |          | Вход "сигнал внешнего прерывания"                        | I      | EXTINT      |

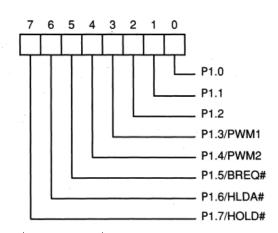

| P1.0                   | 15       | Вход-выход "порт 1, 0 разряд"                            | I/O    |             |

| P1.1                   | 16       | Вход-выход "порт 1, 1 разряд"                            | I/O    |             |

| P1.2                   | 17       | Вход-выход "порт 1, 2 разряд"                            | I/O    |             |

| P1.3                   | 18       | Вход-выход "порт 1, 3 разряд"                            | I/O    |             |

|                        |          | Выход "ШИМ 1"                                            | О      | PWM.1       |

| P1.4                   | 19       | Вход-выход "порт 1, 4 разряд"                            | I/O    |             |

|                        |          | Выход "ШИМ 2"                                            | O      | PWM.2       |

| P1.5                   | 27       | Вход-выход "порт 1, 5 разряд"                            | I/O    |             |

|                        | - '      | Выход "запрос шины"                                      | O      | BREQ#       |

| P1.6                   | 28       | Вход-выход "порт 1, 6 разряд"                            | I/O    | 2122(       |

| 11.0                   | 20       | Выход "подтверждение захвата шины"                       | O      | HLDA#       |

| P1.7                   | 29       | Вход-выход "порт 1, 7 разряд"                            | I/O    | TIEBTIN     |

| 11.7                   | 2)       | Вход "требование захвата шины"                           | I      | HOLD#       |

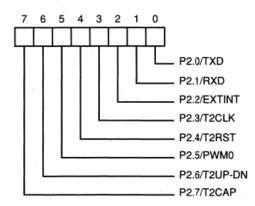

| P2.0                   | 11, 56   | Выход "порт 2, 0 разряд"                                 | 0      | HOLDII      |

| 1 2.0                  | 11, 50   | Выход последовательных данных                            | Ö      | TXD         |

|                        |          | Выход "верификация"*                                     | O      | PVER *      |

| P2.1                   | 10       | Вход "порт 2, 1 разряд"                                  | I      | IVER        |

| 1 4.1                  | 10       | Вход-порт 2, г разряд Вход-выход последовательных данных | I/O/2  | RXD         |

|                        |          | Вход "строб записи"*                                     | I/O/2  | PALE# *     |

| P2.2                   | 7        | 1                                                        | I      | I ALL#      |

| Γ Δ.Δ                  | '        | Вход "порт 2, 2 разряд"                                  |        | EXTINT      |

|                        |          | Вход "сигнал внешнего прерывания"                        | I      |             |

| D2 2                   | 4.4      | Вход "программирование"*                                 | I      | PROG# *     |

| P2.3                   | 44       | Вход "порт 2, 3 разряд"                                  | I      | TOCLE       |

|                        | <u> </u> | Вход "синхронизация таймера 2"                           | I      | T2CLK       |

| 1              | 2   | 3                                                               | 4     | 5        |

|----------------|-----|-----------------------------------------------------------------|-------|----------|

| P2.4           | 42  | Вход "порт 2, 4 разряд"                                         | I     |          |

|                |     | Вход "сброс таймера 2"                                          | I     | T2RST    |

|                |     | Вход "автоинкремент"*                                           | I     | AINC# *  |

| P2.5           | 39  | Выход "порт 2, 5 разряд"                                        | О     |          |

|                |     | Выход "ШИМ 0"                                                   | O     | PWM.0    |

| P2.6           | 30  | Вход-выход "порт 2, 6 разряд"                                   | I/O   |          |

|                |     | Вход "выбор режима таймера 2"                                   | I     | T2UPDN   |

|                |     | Выход "ошибка программирования"*                                | О     | CPVER *  |

| P2.7           | 38  | Вход-выход "порт 2, 7 разряд"                                   | I/O   |          |

|                |     | Вход "выборка данных таймера 2"                                 | I     | T2CAP    |

|                |     | Выход "подтверждение программирования"*                         | Ō     | PACT# *  |

| P3.0           | 67  | Вход-выход "порт 3, 0 разряд"                                   | I/O/2 | 11101    |

| 13.0           | 07  | Вход-выход "адрес-данные, 0 разряд"                             | I/O/Z | AD0      |

| P3.1           | 66  | Вход-выход "порт 3, 1 разряд"                                   | I/O/2 | 7 IDO    |

| 1 3.1          | 00  | Вход-выход порт 3, г разряд Вход-выход "адрес-данные, 1 разряд" | I/O/Z | AD1      |

| P3.2           | 65  | Вход-выход "порт 3, 2 разряд"                                   | I/O/2 | ADI      |

| F 3.2          | 03  | Вход-выход порт 3, 2 разряд Вход-выход "адрес-данные, 2 разряд" | I/O/Z | AD2      |

| D2 2           | (2  |                                                                 |       | ADZ      |

| P3.3           | 63  | Вход-выход "порт 3, 3 разряд"                                   | I/O/2 | 102      |

| D2 4           | (2) | Вход-выход "адрес-данные, 3 разряд"                             | I/O/Z | AD3      |

| P3.4           | 62  | Вход-выход "порт 3, 4 разряд"                                   | I/O/2 | A.D.4    |

| D0.5           | 61  | Вход-выход "адрес-данные, 4 разряд"                             | I/O/Z | AD4      |

| P3.5           | 61  | Вход-выход "порт 3, 5 разряд"                                   | I/O/2 | 155      |

| D0 -           |     | Вход-выход "адрес-данные, 5 разряд"                             | I/O/Z | AD5      |

| P3.6           | 59  | Вход-выход "порт 3, 6 разряд"                                   | I/O/2 |          |

|                |     | Вход-выход "адрес-данные, 6 разряд"                             | I/O/Z | AD6      |

| P3.7           | 58  | Вход-выход "порт 3, 7 разряд"                                   | I/O/2 |          |

|                |     | Вход-выход "адрес-данные, 7 разряд"                             | I/O/Z | AD7      |

| P4.0           | 52  | Вход-выход "порт 4, 0 разряд"                                   | I/O/2 |          |

|                |     | Вход-выход "адрес-данные, 8 разряд"                             | I/O/Z | AD8      |

| P4.1           | 51  | Вход-выход "порт 4, 1 разряд"                                   | I/O/2 |          |

|                |     | Вход-выход "адрес-данные, 9 разряд"                             | I/O/Z | AD9      |

| P4.2           | 50  | Вход-выход "порт 4, 2 разряд"                                   | I/O/2 |          |

|                |     | Вход-выход "адрес-данные, 10 разряд"                            | I/O/Z | AD10     |

| P4.3           | 49  | Вход-выход "порт 4, 3 разряд"                                   | I/O/2 |          |

|                |     | Вход-выход "адрес-данные, 11 разряд"                            | I/O/Z | AD11     |

| P4.4           | 48  | Вход-выход "порт 4, 4 разряд"                                   | I/O/2 |          |

|                |     | Вход-выход "адрес-данные, 12 разряд"                            | I/O/Z | AD12     |

| P4.5           | 47  | Вход-выход "порт 4, 5 разряд"                                   | I/O/2 |          |

|                |     | Вход-выход "адрес-данные, 13 разряд"                            | I/O/Z | AD13     |

| P4.6           | 46  | Вход-выход "порт 4, 6 разряд"                                   | I/O/2 |          |

|                |     | Вход-выход "адрес-данные, 14 разряд"                            | I/O/Z | AD14     |

| P4.7           | 45  | Вход-выход "порт 4, 7 разряд"                                   | I/O/2 |          |

|                |     | Вход-выход "адрес-данные, 15 разряд"                            | I/O/Z | AD15     |

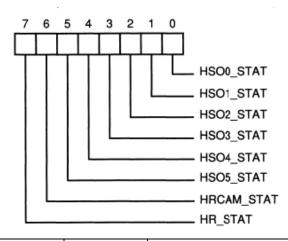

| HSI.0          | 20  | Вход "быстрый ввод, канал 0"                                    | I     |          |

| HSI.1          | 21  | Вход "быстрый ввод, канал 1"                                    | I     |          |

| HSI.2          | 22  | Вход "быстрый ввод, канал 2"                                    | I     |          |

| ·- <del></del> |     | Выход "быстрый вывод, канал 4"                                  | O     | HSO.4    |

| HSI.3          | 24  | Вход "быстрый ввод, канал 3"                                    | I     |          |

|                |     | Выход "быстрый вывод, канал 5"                                  | Ö     | HSO.5    |

| HSO.0          | 25  | Выход "быстрый вывод, канал 0"                                  | 0     |          |

| HSO.1          | 26  | Выход "быстрый вывод, канал 1"                                  | 0     |          |

| -10 0.1        | 20  | 1 22 TOA OBETPENT BELOOM, RUNGET 1                              |       | <u> </u> |

|              | ние таблицы 2           |                                               | 1     |                                         |

|--------------|-------------------------|-----------------------------------------------|-------|-----------------------------------------|

| 1            | 2                       | 3                                             | 4     | 5                                       |

| HSO.2        | 31                      | Выход "быстрый вывод, канал 2"                | O     |                                         |

| HSO.3        | 34                      | Выход "быстрый вывод, канал 3"                | O     |                                         |

| EA#          | 79                      | Вход "внешний доступ"                         | I     |                                         |

| BW           | 71                      | Вход "разрядность внешней шины"               | I     |                                         |

| READY        | 43                      | Вход "готовность"                             | I     |                                         |

| NMI          | 80                      | Вход "немаскируемое прерывание"               | I     |                                         |

| RESET#       | 9                       | Вход-выход "сброс"                            | I/O/2 |                                         |

| INST         | 70                      | Выход "чтение команды"                        | 0     |                                         |

| ALE          | 69                      | Выход "разрешение записи адреса"              | 0     |                                         |

|              |                         | Выход "адрес действителен"                    | О     | ADV#                                    |

| WR#          | 40                      | Выход "запись"                                | 0     |                                         |

|              |                         | Выход "запись младшего байта"                 | O     | WRL#                                    |

| BHE#         | 41                      | Выход "разрешение записи старшего байта"      | 0     |                                         |

|              |                         | Выход "запись старшего байта"                 | Ö     | WRH#                                    |

| RD#          | 68                      | Выход "чтение"                                | 0     | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |

| CLKOUT       | 72                      | Выход "системный тактовый сигнал"             | 0     |                                         |

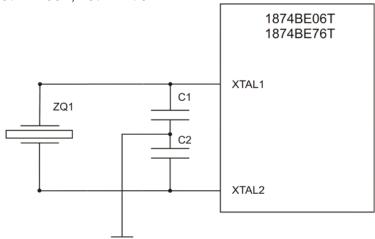

| XTAL1        | 74                      | Вывод подключения кварцевого резонатора/      | _     |                                         |

| AIALI        | /                       | вход тактового сигнала                        |       |                                         |

| XTAL2        | 73                      | Вывод подключения кварцевого резонатора       | _     |                                         |

| VPP          | 37                      | Вход "возврат из режима пониженного           | _     |                                         |

| VPP          | 37                      | потребления"                                  | I     |                                         |

|              |                         | Вывод "напряжение программирования"           | 1     |                                         |

| #V/CC1       | 9 22 60                 |                                               | _     |                                         |

| #VCC1        | 8, 33, 60,<br>77, 78    | Питание 5 В цифровой части микросхемы         | _     |                                         |

| ∩VCC2        | 5                       | Питание 5 В аналоговой части микросхемы       | _     |                                         |

| #0V          | 6, 12, 32,              | Общий вывод цифровой части микросхемы         | _     |                                         |

|              | 35, 36, 53, 55, 57, 64, |                                               |       |                                         |

|              | 75, 76                  |                                               |       |                                         |

| ∩0V          | 3, 4                    | Общий вывод аналоговой части микросхемы       | _     |                                         |

| * To         | —<br>Элько для мик      | сросхемы 1874ВЕ76Т.                           |       |                                         |

|              | , ,                     | Для микросхемы 1874ВЕ05Т                      |       |                                         |

| 1            | 2                       | 3                                             | 4     | 5                                       |

| P0.0         | 84                      | Вход "порт 0, 0 разряд"                       | Ī     |                                         |

| P0.1         | 83                      | Вход "порт 0, 1 разряд"                       | I     | 1                                       |

| P0.2         | 85                      | Вход "порт 0, 2 разряд"                       | I     |                                         |

| P0.3         | 82                      | Вход "порт 0, 3 разряд"                       | I     |                                         |

| P0.4         | 2                       | Вход порт 0, 3 разряд Вход "порт 0, 4 разряд" | I     |                                         |

| P0.5         | 1                       | Вход "порт 0, 5 разряд"                       | I     |                                         |

| P0.6         | 86                      | Вход порт 0, 5 разряд Вход "порт 0, 6 разряд" | I     |                                         |

| P0.7         | 87                      |                                               | I     |                                         |

| PU. /        | 87                      | Вход "порт 0, 7 разряд"                       |       | EVTINT                                  |

| D1 ()        | 15                      | Вход "сигнал внешнего прерывания"             | I     | EXTINT                                  |

| P1.0         | 15                      | Вход-выход "порт 1, 0 разряд"                 | I/O   |                                         |

| P1.1         | 16                      | Вход-выход "порт 1, 1 разряд"                 | I/O   |                                         |

| P1.2         | 17                      | Вход-выход "порт 1, 2 разряд"                 | I/O   |                                         |

| P1.3         | 18                      | Вход-выход "порт 1, 3 разряд"                 | I/O   | DIVID 6 4                               |

| <b>5.1</b> · | 10                      | Выход "ШИМ 1"                                 | 0     | PWM.1                                   |

| P1.4         | 19                      | Вход-выход "порт 1, 4 разряд"                 | I/O   |                                         |

|              |                         | Выход "ШИМ 2"                                 | О     | PWM.2                                   |

| 1     | 2          | 3                                    | 4              | 5              |

|-------|------------|--------------------------------------|----------------|----------------|

| P1.5  | 27         | Вход-выход "порт 1, 5 разряд"        | I/O            |                |

|       |            | Выход "запрос шины"                  | О              | BREQ#          |

| P1.6  | 28         | Вход-выход "порт 1, 6 разряд"        | I/O            |                |

|       |            | Выход "подтверждение захвата шины"   | О              | HLDA#          |

| P1.7  | 29         | Вход-выход "порт 1, 7 разряд"        | I/O            |                |

|       |            | Вход "требование захвата шины"       | I              | HOLD#          |

| P2.0  | 11, 56     | Выход "порт 2, 0 разряд"             | 0              |                |

| 1 2.0 | 11,00      | Выход последовательных данных        | O              | TXD            |

| P2.1  | 10         | Вход "порт 2, 1 разряд"              | I              |                |

|       |            | Вход-выход последовательных данных   | I/O/2          | RXD            |

| P2.2  | 7          | Вход "порт 2, 2 разряд"              | I              | 10.10          |

| 1 2.2 | ,          | Вход внешнего прерывания             | Ī              | EXTINT         |

| P2.3  | 44         | Вход "порт 2, 3 разряд"              | I              | DITIII (I      |

| 1 2.3 |            | Вход "синхронизация таймера 2"       | I              | T2CLK          |

| P2.4  | 42         | Вход "порт 2, 4 разряд"              | I              | TECLIK         |

| 1 2.7 | 72         | Вход "сброс таймера 2"               | I              | T2RST          |

| P2.5  | 39         | Выход "порт 2, 5 разряд"             | 0              | 12101          |

| 1 2.3 | 37         | Выход "ШИМ 0"                        | O              | PWM.0          |

| P2.6  | 30         | Вход-выход "порт 2, 6 разряд"        | I/O            | 1 ** 1 * 1 . 0 |

| 1 2.0 | 30         | Вход "выбор режима таймера 2"        | I              | T2UPDN         |

| P2.7  | 38         | Вход-выход "порт 2, 7 разряд"        | I/O            | 120101         |

| F2./  | 36         | Вход "выборка данных таймера 2"      | I              | T2CAP          |

| P3.0  | 67         |                                      | I/O/2          | 12CAF          |

| P3.0  | 67         | Вход-выход "порт 3, 0 разряд"        | I/O/Z<br>I/O/Z | 4 D0           |

| D2 1  |            | Вход-выход "адрес-данные, 0 разряд"  | I/O/2          | AD0            |

| P3.1  | 66         | Вход-выход "порт 3, 1 разряд"        | I/O/Z<br>I/O/Z | A D 1          |

| D2 2  | <i>C</i> 5 | Вход-выход "адрес-данные, 1 разряд"  |                | AD1            |

| P3.2  | 65         | Вход-выход "порт 3, 2 разряд"        | I/O/2          | 100            |

| D2 2  | 62         | Вход-выход "адрес-данные, 2 разряд"  | I/O/Z          | AD2            |

| P3.3  | 63         | Вход-выход "порт 3, 3 разряд"        | I/O/2          | 102            |

| D2 4  |            | Вход-выход "адрес-данные, 3 разряд"  | I/O/Z          | AD3            |

| P3.4  | 62         | Вход-выход "порт 3, 4 разряд"        | I/O/2          | 101            |

| D0 5  | <i>C</i> 1 | Вход-выход "адрес-данные, 4 разряд"  | I/O/Z          | AD4            |

| P3.5  | 61         | Вход-выход "порт 3, 5 разряд"        | I/O/2          | 155            |

| D0 (  |            | Вход-выход "адрес-данные, 5 разряд"  | I/O/Z          | AD5            |

| P3.6  | 59         | Вход-выход "порт 3, 6 разряд"        | I/O/2          | 100            |

|       |            | Вход-выход "адрес-данные, 6 разряд"  | I/O/Z          | AD6            |

| P3.7  | 58         | Вход-выход "порт 3, 7 разряд"        | I/O/2          |                |

|       |            | Вход-выход "адрес-данные, 7 разряд"  | I/O/Z          | AD7            |

| P4.0  | 52         | Вход-выход "порт 4, 0 разряд"        | I/O/2          |                |

|       |            | Вход-выход "адрес-данные, 8 разряд"  | I/O/Z          | AD8            |

| P4.1  | 51         | Вход-выход "порт 4, 1 разряд"        | I/O/2          |                |

|       |            | Вход-выход "адрес-данные, 9 разряд"  | I/O/Z          | AD9            |

| P4.2  | 50         | Вход-выход "порт 4, 2 разряд"        | I/O/2          |                |

|       |            | Вход-выход "адрес-данные, 10 разряд" | I/O/Z          | AD10           |

| P4.3  | 49         | Вход-выход "порт 4, 3 разряд"        | I/O/2          |                |

|       |            | Вход-выход "адрес-данные, 11 разряд" | I/O/Z          | AD11           |

| P4.4  | 48         | Вход-выход "порт 4, 4 разряд"        | I/O/2          |                |

|       |            | Вход-выход "адрес-данные, 12 разряд" | I/O/Z          | AD12           |

## Окончание таблицы 2.1

| 1      | 2            | 3                                        | 4     | 5     |

|--------|--------------|------------------------------------------|-------|-------|

| P4.5   | 47           | Вход-выход "порт 4, 5 разряд"            | I/O/2 |       |

|        |              | Вход-выход "адрес-данные, 13 разряд"     | I/O/Z | AD13  |

| P4.6   | 46           | Вход-выход "порт 4, 6 разряд"            | I/O/2 |       |

|        |              | Вход-выход "адрес-данные, 14 разряд"     | I/O/Z | AD14  |

| P4.7   | 45           | Вход-выход "порт 4, 7 разряд"            | I/O/2 |       |

|        |              | Вход-выход "адрес-данные, 15 разряд"     | I/O/Z | AD15  |

| HSI.0  | 20           | Вход "быстрый ввод, канал 0"             | I     |       |

| HSI.1  | 21           | Вход "быстрый ввод, канал 1"             | I     |       |

| HSI.2  | 22           | Вход "быстрый ввод, канал 2"             | I     |       |

|        |              | Выход "быстрый вывод, канал 4"           | O     | HSO.4 |

| HSI.3  | 24           | Вход "быстрый ввод, канал 3"             | I     |       |

|        |              | Выход "быстрый вывод, канал 5"           | O     | HSO.5 |

| HSO.0  | 25           | Выход "быстрый вывод, канал 0"           | O     |       |

| HSO.1  | 26           | Выход "быстрый вывод, канал 1"           | O     |       |

| HSO.2  | 31           | Выход "быстрый вывод, канал 2"           | О     |       |

| HSO.3  | 34           | Выход "быстрый вывод, канал 3"           | О     |       |

| EA#    | 79           | Вход "внешний доступ"                    | I     |       |

| BW     | 71           | Вход "разрядность внешней шины"          | I     |       |

| READY  | 43           | Вход "готовность"                        | I     |       |

| NMI    | 80           | Вход "немаскируемое прерывание"          | I     |       |

| RESET# | 9            | Вход-выход "сброс"                       | I/O/2 |       |

| INST   | 70           | Выход "чтение команды"                   | О     |       |

| ALE    | 69           | Выход "разрешение записи адреса"         | О     |       |

|        |              | Выход "адрес действителен"               | O     | ADV#  |

| WR#    | 40           | Выход "запись"                           | О     |       |

|        |              | Выход "запись младшего байта"            | O     | WRL#  |

| BHE#   | 41           | Выход "разрешение записи старшего байта" | O     |       |

|        |              | Выход "запись старшего байта"            | O     | WRH#  |

| RD#    | 68           | Выход "чтение"                           | O     |       |

| CLKOUT | 72           | Выход "системный тактовый сигнал"        | O     |       |

| XTAL1  | 74           | Вывод подключения кварцевого резонатора/ | _     |       |

|        |              | вход тактового сигнала                   | I     |       |

| XTAL2  | 73           | Вывод подключения кварцевого             | _     |       |

|        |              | резонатора.                              |       |       |

| VPP    | 37           | Вход "возврат из режима пониженного      | I     |       |

|        |              | потребления "                            |       |       |

| VCC1   | 8, 33, 60,   | Питание периферии микросхемы             | _     |       |

|        | 77, 78       |                                          |       |       |

| VCC2   | 5            | Питание ядра микросхемы                  | _     |       |

| 0V     | 3, 4, 6, 12, | Общий вывод микросхемы                   | _     |       |

|        | 32, 35, 36,  |                                          |       |       |

|        | 53, 55, 57,  |                                          |       |       |

|        | 64, 75, 76   |                                          |       |       |

Примечания

<sup>1</sup> Выводы 13, 14, 23, 54, 81, 88 – свободные, не используются.

<sup>2</sup> В графе «Тип вывода»: I – вход, O – выход, Z – третье состояние, 2 – режим открытого стока.

#### 2.2 Электрические параметры микросхем

Электрические параметры микросхем при приёмке и поставке и предельно-допустимые значения параметров приведены в таблицах 2.2 и 2.3 соответственно.

Номинальное значение напряжения питания микросхем 1874BE76T и 1874BE06T 5,0 В. Допустимое отклонение напряжения питания  $\pm 10$  %. Амплитуда пульсаций напряжения питания не более 50 мВ. Напряжение источника опорного напряжения от 4,0 до 5,5 В. Допустимое отклонение напряжения питания от крайних значений минус 1 % для напряжения 4,0 В и плюс 1 % для напряжения 5,5 В.

Номинальное значение напряжения питания ядра микросхемы 1874BE05T должно быть 3,3 В. Номинальное значение напряжения питания периферии микросхемы должно быть 5,0 В или 3,3 В. Допустимое отклонение напряжения питания ядра от номинального должно быть не более  $\pm$  0,3 В, периферии – не более  $\pm$  0,5 В при  $U_{CC1}=5,0$  В или не более  $\pm$  0,3 В при  $U_{CC1}=3,3$  В. Амплитудное значение пульсации напряжения питания ядра должно быть не более 30 мВ, периферии – не более 50 мВ (при  $U_{CC1}=5,0$  В) или не более 30 мВ (при  $U_{CC1}=3,3$  В).

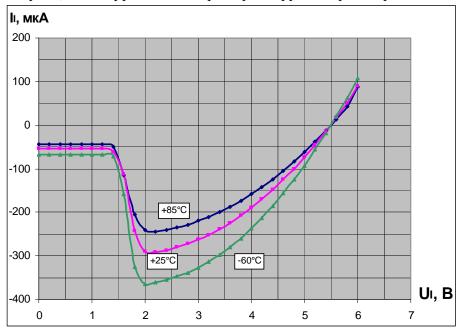

Микросхемы устойчивы к климатическим воздействиям и будут сохранять свои параметры в процессе и после воздействия на них климатических факторов, приведенных в таблице 4 ОСТ В 11 0998-99, в том числе:

- пониженной рабочей температуры среды минус 60 °C;

- повышенной рабочей температуры среды 85 °C;

- повышенной предельной температуры 150 °C.

Таблица 2.2 – Электрические параметры при приёмке и поставке в диапазоне рабочих температур окружающей среды от минус 60 °C до плюс 85 °C

| Наименование параметра,                | Буквен-                    | Норма          |          | Режим                       |

|----------------------------------------|----------------------------|----------------|----------|-----------------------------|

| единица измерения                      | начение                    | не менее       | не более | измерения                   |

|                                        | парметра                   |                |          |                             |

| 1                                      | 2                          | 3              | 4        | 5                           |

| Для микросхем 18                       | 74ВЕ76Т и                  | 1874BE06       | Γ        |                             |

| 1 Выходное напряжение низкого уровня   | $\mathrm{U}_{\mathrm{OL}}$ |                |          | $I_{OL} = 2.8 \text{ MA},$  |

| по выводам, В                          |                            | _              | 0,45     | $U_{CC1} = 4.5 B$           |

| 2 Выходное напряжение высокого уровня  | $U_{\mathrm{OH1}}$         |                |          | $I_{OH} = -30$ мкA,         |

| по выводам Р1.0 – Р1.7, 2.6, Р2.7, В   |                            | $U_{CC1}$ -0,7 | _        | $U_{CC1} = 4.5 B$           |

| 3 Выходное напряжение высокого         | $\rm U_{OH2}$              |                |          |                             |

| уровня по выводам RD#, WR#, ALE,       |                            |                |          |                             |

| BHE#, INST, HSO.0 – HSO.3,             |                            |                |          | $I_{OH} = -3.2 \text{ MA},$ |

| PWM.0/P2.5, CLKOUT, AD0/P3.0 –         |                            |                |          | $U_{CC1} = 4.5 B$           |

| AD7/P3.7, AD8/P4.0 – AD15/P4.7,        |                            |                |          |                             |

| TXD/P2.0, RXD/P2.1 (в режиме 0), В     |                            | $U_{CC1}$ -0,7 | _        |                             |

| 4 Токи утечки низкого уровня на входе, | $I_{ILL1}$                 |                |          | $U_{IL} = 0 B$              |

| кроме выводов P0.0 – P0.7, RESET#, мкА |                            | -10            | _        | $U_{CC1} = 5.5 \text{ B}$   |

| Продолжение таблицы 2.2                                                                                                    |                           |      |     |                                                           |  |

|----------------------------------------------------------------------------------------------------------------------------|---------------------------|------|-----|-----------------------------------------------------------|--|

| 1                                                                                                                          | 2                         | 3    | 4   | 5                                                         |  |

| 5 Токи утечки высокого уровня на входе,                                                                                    | $I_{ILH1}$                |      |     | $U_{IH} = (U_{CC1} - 0.3) B,$                             |  |

| кроме выводов P0.0 – P0.7, NMI, мкА                                                                                        |                           | _    | 10  | $U_{CC1} = 5.5 B$                                         |  |

| 6 Токи утечки низкого уровня на входе                                                                                      | I <sub>ILL2</sub>         |      |     | $U_{IL} = 0 B$ ,                                          |  |

| по выводам Р0.0 – Р0.7, мкА                                                                                                |                           | -3   | _   | $U_{CC1} = 5.5 B$                                         |  |

| 7 Токи утечки высокого уровня на входе                                                                                     | $I_{ILH2}$                |      |     | $U_{IH} = U_{CC1} =$                                      |  |

| по выводам Р0.0 – Р0.7, мкА                                                                                                |                           | _    | 3   | $= U_{CC2} = 5,5 B$                                       |  |

| 8 Входной ток низкого уровня по                                                                                            | ${ m I}_{ m IL}$          |      |     | $U_{IL} = 0.45 \text{ B}$                                 |  |

| выводам Р1.0 – Р1.7, Р2.6, Р2.7, мкА                                                                                       |                           | -70  | _   | O <sub>IL</sub> = 0,43 B                                  |  |

| 9 Входной ток высокого уровня по                                                                                           | $I_{IH}$                  |      |     | $U_{IH} = 2,0 B,$                                         |  |

| выводам Р1.0 – Р1.7, Р2.6, Р2.7, мкА                                                                                       |                           | -650 | _   | $U_{CC1} = 5.5 \text{ B}$                                 |  |

| 10 Динамический ток потребления в                                                                                          | $I_{OCC1}$                |      |     | $U_{\mathrm{VPP}} = U_{\mathrm{CC1}} =$                   |  |

| режиме RESET цифровой части ИМС по                                                                                         |                           |      |     | $= U_{CC2} = 5.5 B,$                                      |  |

| выводам VCC1, мА                                                                                                           |                           | _    | 100 | $f_{CI} = 12 M\Gamma$ ц                                   |  |

| 11 Динамический ток потребления                                                                                            | $I_{OCC2}$                |      |     | $\mathrm{U}_{\mathrm{VPP}} = \mathrm{U}_{\mathrm{CC1}} =$ |  |

| аналоговой части ИМС по выводу VCC2,                                                                                       |                           |      |     | $= U_{CC2} = 5.5 B,$                                      |  |

| мА                                                                                                                         |                           | _    | 10  | $f_{CI} = 12 M\Gamma$ ц                                   |  |

| 12 Функциональный контроль                                                                                                 | ΦК                        | _    | _   | $U_{CC1} = (4,5; 5,5) B,$                                 |  |

|                                                                                                                            |                           |      |     | $U_{CC2} = (4,0; 5,5) B,$                                 |  |

|                                                                                                                            |                           |      |     | $f_{CI} = (8,0; 20) M\Gamma$ ц                            |  |

| 13 Время переключения сигнала                                                                                              |                           |      |     |                                                           |  |

| на выходе CLKOUT:                                                                                                          |                           | _    |     |                                                           |  |

| - время нарастания, нс                                                                                                     | $t_r$                     |      | 27  |                                                           |  |

| - время спада, нс                                                                                                          | $\mathbf{t}_{\mathrm{f}}$ |      | 27  |                                                           |  |

| Примечание — Параметры $I_{ILL1}$ , $I_{ILH1}$ , $I_{ILL2}$ , $I_{ILH2}$ , $I_{IL}$ , $I_{IH}$ при температуре минус 60 °C |                           |      |     |                                                           |  |

Примечание — Параметры  $I_{ILL1}$ ,  $I_{ILH1}$ ,  $I_{ILL2}$ ,  $I_{ILH2}$ ,  $I_{IL}$ ,  $I_{IH}$  при температуре минус 60 °C не измеряются, а гарантируются нормой при температуре (25 $\pm$ 10) °C.

| Для микросхемы 1874ВЕ05Т                   |                 |             |      |                                                    |  |  |

|--------------------------------------------|-----------------|-------------|------|----------------------------------------------------|--|--|

| 14 Выходное напряжение низкого             | U <sub>OL</sub> |             |      | $I_{OL} = 2.8 \text{ mA},$                         |  |  |

| уровня по выводам, В                       |                 | _           | 0,45 | $U_{CC1} = 5.5 \text{ B}, U_{CC2} = 3.0 \text{ B}$ |  |  |

| 15 Выходное напряжение высокого            | $U_{OH1}$       |             |      | $I_{OH} = -30 \text{ MKA},$                        |  |  |

| уровня по выводам Р1.0 – Р1.7, Р2.6,       |                 | $U_{CC1}$   |      | $U_{CC1}^{1)} = U_{CC2} = 3.0 \text{ B}$           |  |  |

| P2.7, B                                    |                 | -0,7        | _    | OCC1 = OCC2 = 3,0  B                               |  |  |

| 16 Выходное напряжение высокого            | $U_{OH2}$       |             |      |                                                    |  |  |

| уровня по выводам: RD#, WR#, ALE,          |                 |             |      |                                                    |  |  |

| BHE#, INST, HSO, PWM.0/P2.5,               |                 |             |      | $I_{OH} = -3.2 \text{ MA},$                        |  |  |

| CLKOUT, AD0/P3.0 – AD7/P3.7,               |                 |             |      | $U_{CC1}^{(1)} = U_{CC2} = 3.0 \text{ B}$          |  |  |

| AD8/P4.0 – AD15/P4.7, TXD/P2.0,            |                 | $U_{CC1}$   |      |                                                    |  |  |

| RXD/P2.1 (в режиме 0), В                   |                 | -0,7        | _    |                                                    |  |  |

| 17 Токи утечки низкого уровня              | $I_{ILL1}$      |             |      | $U_{II} = 0 B$                                     |  |  |

| на входах, кроме P0.0 – P0.7, P1.0 – P1.7, |                 |             |      | $U_{CC1} = 5.5 \text{ B}$                          |  |  |

| P2.6, P2.7, RESET#, мкА                    |                 | -10         | _    | OCC1 = 3,3 B                                       |  |  |

| 18 Токи утечки высокого уровня             | $I_{ILH1}$      |             |      | $U_{IH} = 5.2 \text{ B}$                           |  |  |

| на входах, кроме P0.0 – P0.7, P1.0 – P1.7, |                 |             |      | $U_{CC1} = 5.5 \text{ B}$                          |  |  |

| P2.6, P2.7, NMI, мкА                       |                 | _           | 10   | OCC1 = 3,3 B                                       |  |  |

| 19 Токи утечки низкого уровня              | $I_{ILL2}$      |             |      | $U_{IL} = 0 B, U_{CC1} = 5.5 B,$                   |  |  |

| на входах Р0.0 – Р0.7, мкА                 |                 | -3          | _    | $U_{CC2} = 3,6 \text{ B}$                          |  |  |

| 20 Токи утечки высокого уровня             | $I_{ILH2}$      |             |      | $U_{IH} = U_{CC1} = 5.5 B,$                        |  |  |

| на входах Р0.0 – Р0.7, мкА                 |                 | _           | 3    | $U_{CC2} = 3,6 \text{ B}$                          |  |  |

| 21 Входной ток низкого уровня по           | $I_{IL}$        |             |      | $U_{IL} = 0.45 B,$                                 |  |  |

| выводам Р1.0 – Р1.7, Р2.6, Р2.7, мкА       |                 | <b>- 90</b> | _    | $U_{CC1} = 5.5 \text{ B}, U_{CC2} = 3.6 \text{ B}$ |  |  |

Окончание таблицы 2.2

| окон шине таолицы 2.2                |                  |      |    |                                                           |

|--------------------------------------|------------------|------|----|-----------------------------------------------------------|

| 1                                    | 2                | 3    | 4  | 5                                                         |

| 22 Входной ток высокого уровня по    | ${ m I}_{ m IH}$ |      |    | $U_{IH} = 2.0 \text{ B}, U_{CC1} =$                       |

| выводам Р1.0 – Р1.7, Р2.6, Р2.7, мкА |                  | -650 | _  | $= 5.5 \text{ B}, \text{ U}_{\text{CC2}} = 3.6 \text{ B}$ |

| 23 Динамический ток потребления      | $I_{OCC1}$       |      |    | $U_{CC1} = 5.5 B,$                                        |

| периферии ИМС по выводам VCC1        |                  |      |    | $U_{CC2} = 3.6 B,$                                        |

| в режиме RESET, мА                   |                  | _    | 60 | $f_{CI} = 12 M\Gamma$ ц                                   |

| 24 Динамический ток потребления      | $I_{OCC2}$       |      |    | $U_{CC1} = 5.5 B,$                                        |

| ядра ИМС по выводу VCC2 в            |                  |      |    | $U_{CC2} = 3.6 B,$                                        |

| режиме RESET, мА                     |                  | _    | 40 | $f_{CI} = 12 M\Gamma$ ц                                   |

| 25 Динамический ток потребления      | $I_{OCC}$        |      |    | $U_{CC1}^{(1)} = U_{CC2} = 3.6 \text{ B},$                |

| периферии и ядра ИМС по выводам      |                  |      |    | $f_{CI} = 12 M\Gamma$ ц                                   |

| VCC1, VCC2 в режиме RESET, мА        |                  | _    | 45 | ICI — 12 IVII Ц                                           |

| 26 Функциональный контроль           | ФК               | _    | _  | $U_{CC1} = (3,0^{1}); 5,5) B,$                            |

|                                      |                  |      |    | $U_{CC2} = (3,0; 3,6) B,$                                 |

|                                      |                  |      |    | $f_{CI} = (8,0; 20) M\Gamma$ ц                            |

| 27 Время переключения сигнала        |                  |      |    |                                                           |

| на выходе CLKOUT:                    |                  |      |    | $U_{CC1}^{(1)} = U_{CC2} = 3.0 B,$                        |

| - время нарастания, нс               | $t_{\rm r}$      | _    | 24 | $f_{CI} = 8 M \Gamma$ ц                                   |

| - время спада, нс                    | $t_{\mathrm{f}}$ |      | 24 |                                                           |

Примечание — Параметры  $I_{ILL1}$ ,  $I_{ILH1}$ ,  $I_{ILL2}$ ,  $I_{ILH2}$ ,  $I_{IL}$ ,  $I_{IH}$  при температуре минус 60 °C не измеряются, а гарантируются нормой при температуре (25 $\pm$ 10) °C.

Таблица 2.3 – Значения предельно-допустимых электрических режимов эксплуатации в диапазоне рабочих температур

| Наименование параметра режима,<br>единица измерения | Буквенное обозначе-<br>ние  | Предельно-<br>допустимый<br>режим |               | •        | льный<br>ким    |

|-----------------------------------------------------|-----------------------------|-----------------------------------|---------------|----------|-----------------|

|                                                     | параметра                   | не менее                          | не более      | не менее | не более        |

| 1                                                   | 2                           | 3                                 | 4             | 5        | 6               |

| Для микросхем                                       | 1874BE76T                   | и 1874ВЕО                         | 6T            |          |                 |

| 1 Напряжение питания цифровой части                 | $U_{CC1}$                   |                                   |               |          |                 |

| ИМС, В                                              |                             | 4,5                               | 5,5           | _        | 7,0             |

| 2 Напряжение питания аналоговой части               | $U_{CC2}$                   |                                   |               |          |                 |

| ИМС, В                                              |                             | 4,0                               | 5,5           | _        | 7,0             |

| 3 Напряжение программирования                       | $\mathrm{U}_{\mathrm{VPP}}$ |                                   |               |          |                 |

| внутреннего OTPROM по выводам VPP,                  | $\mathrm{U}_{\mathrm{EA}}$  |                                   |               |          |                 |

| EA#, B                                              |                             | 12,25                             | 12,75         | _        | 13,0            |

| (только для ИМС 1874ВЕ76Т)                          |                             |                                   |               |          |                 |

| 4 Входное напряжение низкого уровня, В              | $U_{\mathrm{IL}}$           | -0,5                              | 0,8           | -0,6     | _               |

| 5 Входное напряжение высокого уровня                | $U_{IHCI}$                  |                                   |               |          |                 |

| тактового сигнала XTAL1, В                          |                             | $0,7~\mathrm{U}_{\mathrm{CC1}}$   | $U_{CC1}+0,5$ | _        | $U_{CC1} + 0,6$ |

| 6 Входное напряжение высокого уровня                | U <sub>IHRESET</sub>        |                                   |               |          |                 |

| по выводу RESET#, В                                 |                             | 2,2                               | $U_{CC1}+0,5$ | _        | $U_{CC1} + 0,6$ |

| 7 Входное напряжение высокого                       | $U_{\mathrm{IH}}$           |                                   |               |          |                 |

| уровня, В                                           |                             | $0,2U_{CC1}+1,0$                  | $U_{CC1}+0,5$ | _        | $U_{CC1} + 0,6$ |

$<sup>^{1)}</sup>$  При номинальном напряжении питания  $U_{CC1}=U_{CC2}=(3,3\pm0,3)$  В выводы питания периферии и ядра запитываются от одного источника ( $U_{CC2}$ ).

#### Окончание таблицы 2.3

| 1                                     |                                                                                                                                            |                            | 3                | 4             | 5    | 6             |

|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------------------|---------------|------|---------------|

| ток<br>высокого                       | RD#, WR#, ALE, BHE#, INST, HSO, PWM.0/P2.5, CLKOUT, AD0/P3.0 – AD7/P3.7, AD8/P4.0 – AD15/P4.7, TXD/P2.0, RXD/P2.1 (в режиме 0)             | $I_{\mathrm{OH}}$          | -3,2             | -             | -10  | _             |

| уровня, мА                            | ,                                                                                                                                          | T                          | -0,03            | 2.0           | -0,1 | 10            |

|                                       | й ток низкого уровня, мА                                                                                                                   | I <sub>OL</sub>            | _                | 2,8           | _    | 10            |

|                                       | следования импуль-сов                                                                                                                      | $f_{CI}$                   | 0                | 20            |      |               |

| -                                     | игнала, МГц                                                                                                                                |                            | 8                | 20            | _    | _             |

| , ,                                   | ность фронтов тактового                                                                                                                    | $t_{LH}, t_{HL}$           |                  | _             |      |               |

| сигнала, нс                           |                                                                                                                                            |                            | _                | 5             | _    | -             |

| 12 Емкость                            | нагрузки, пФ                                                                                                                               | $C_L$                      |                  | 100           | _    | 200           |

|                                       | Для микросхемы                                                                                                                             | л 1874BE                   |                  |               |      | 1             |

| 13 Напряже                            | ение питания периферии ИМС, В                                                                                                              | $U_{CC1}$                  | 4,5              | 5,5           | _    | 6,0           |

|                                       |                                                                                                                                            |                            | 3,0              | 3,6           |      | 0,0           |

| 14 Напряже                            | ение питания ядра ИМС, В                                                                                                                   | $U_{CC2}$                  | 3,0              | 3,6           | _    | 4,0           |

| 15 Входное                            | напряжение низкого уровня, В                                                                                                               | $\mathrm{U}_{\mathrm{IL}}$ | 0                | 0,8           | -0,5 | _             |

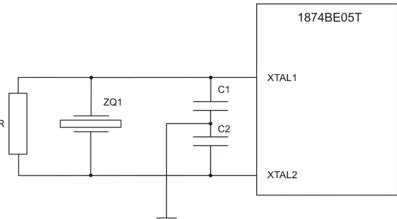

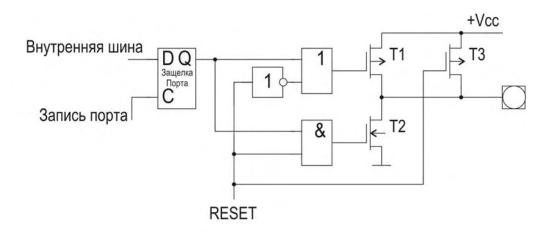

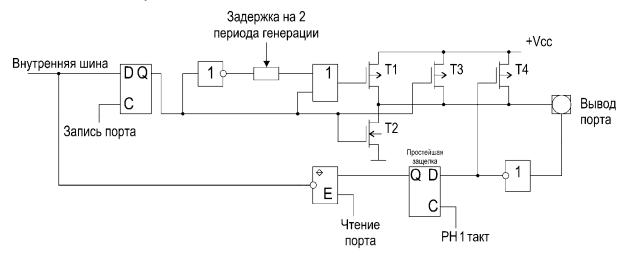

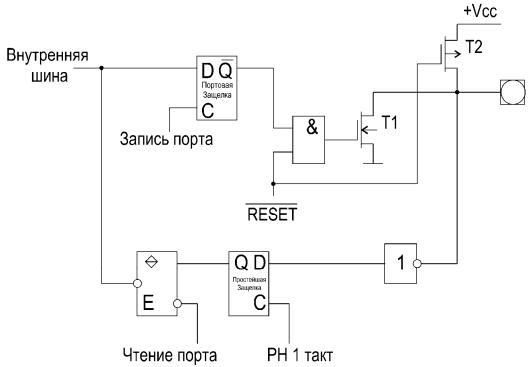

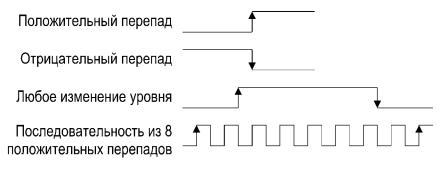

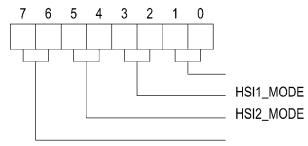

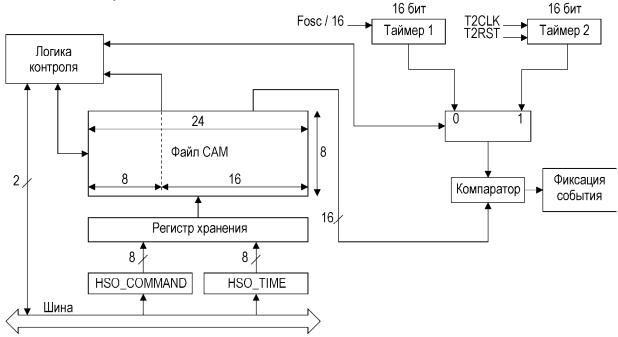

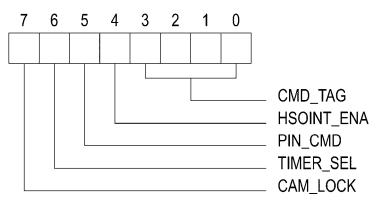

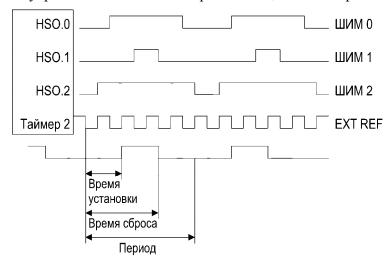

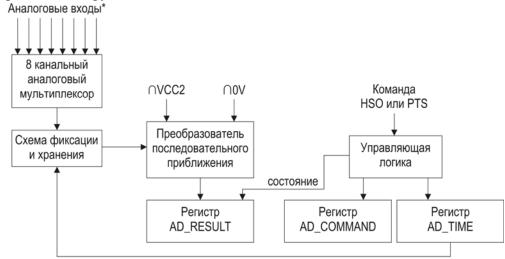

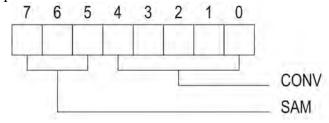

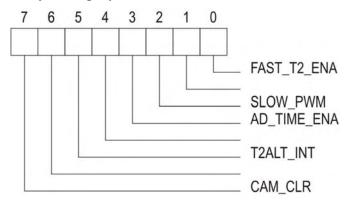

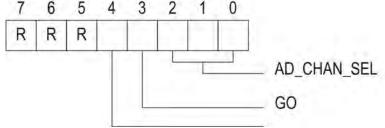

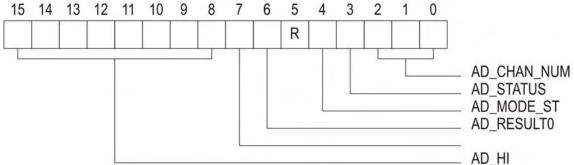

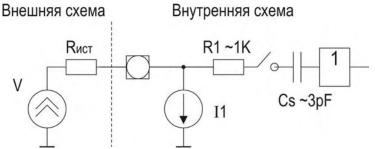

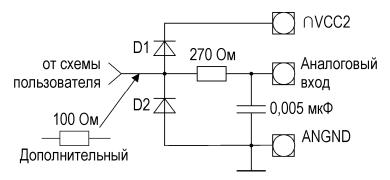

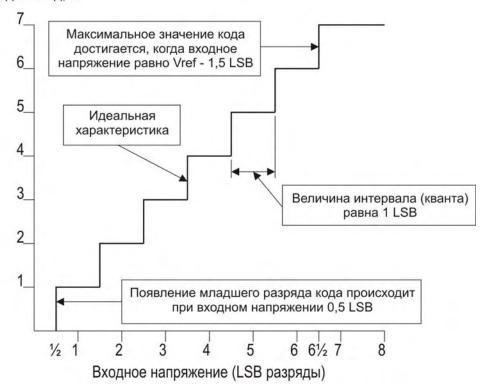

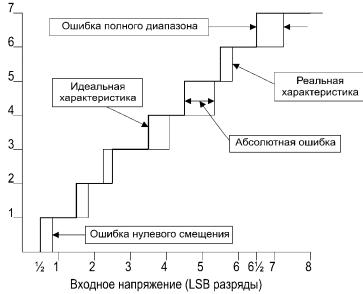

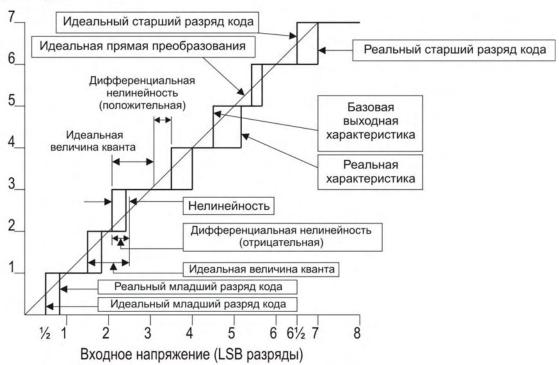

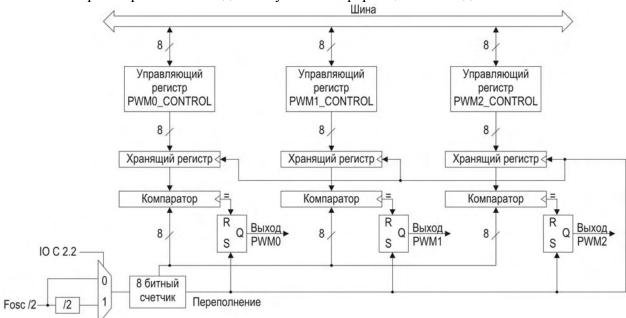

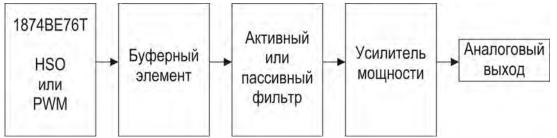

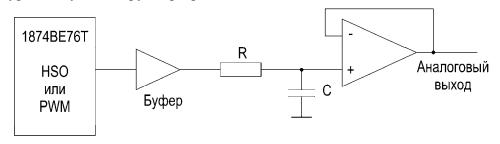

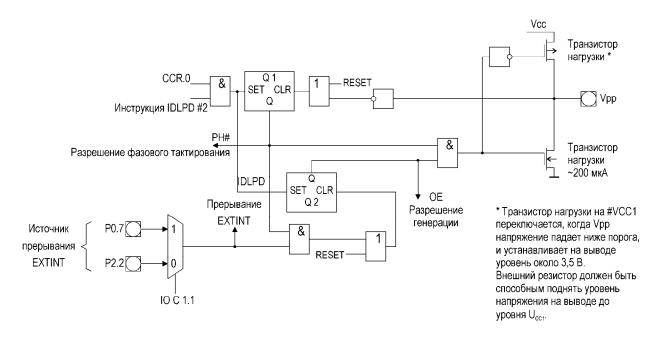

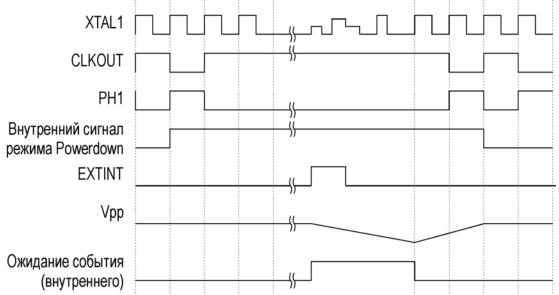

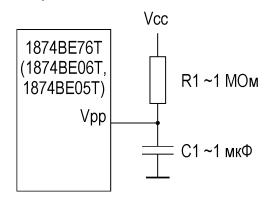

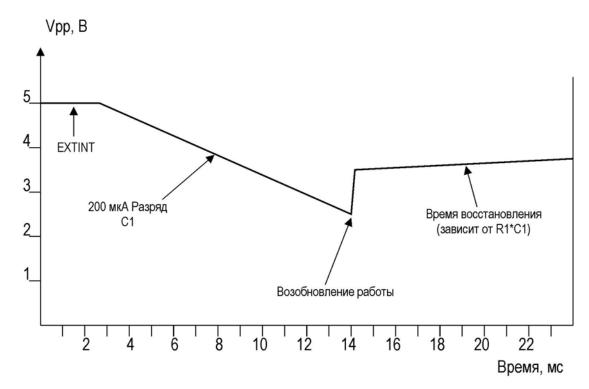

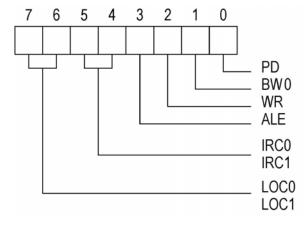

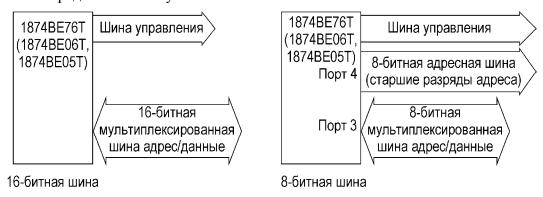

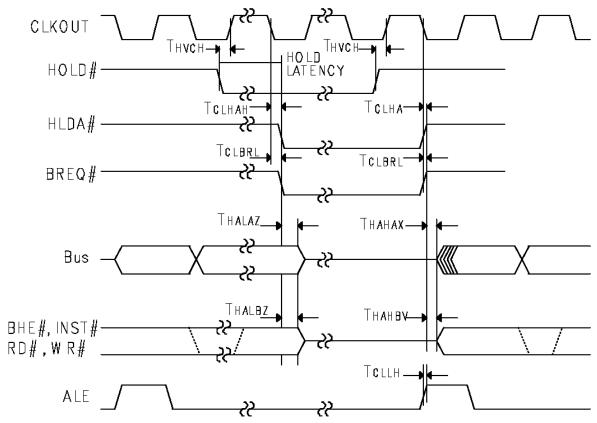

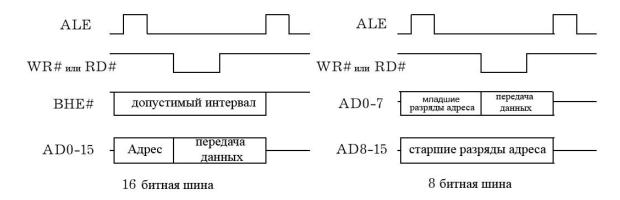

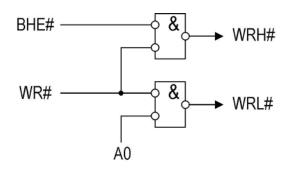

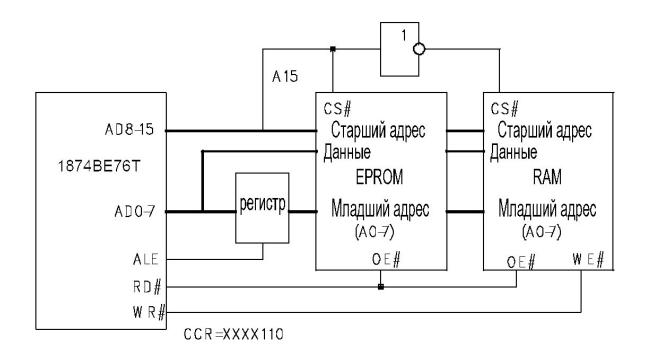

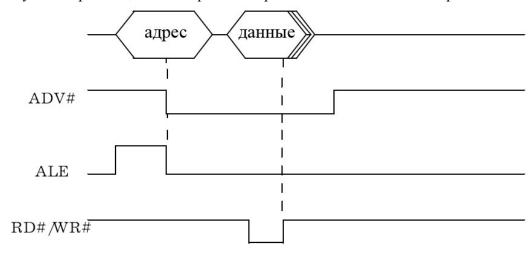

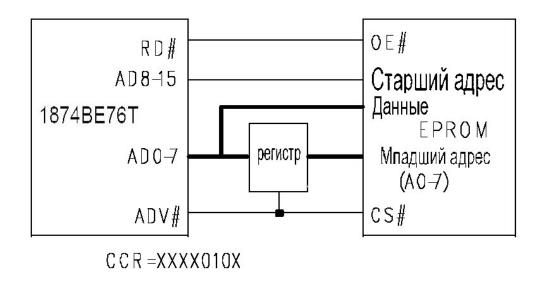

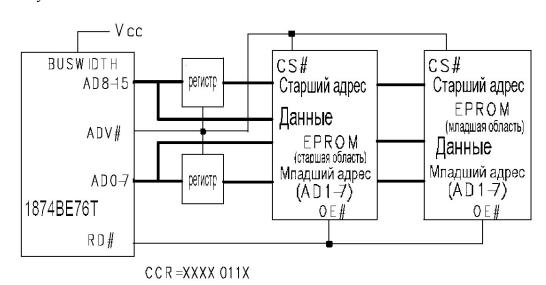

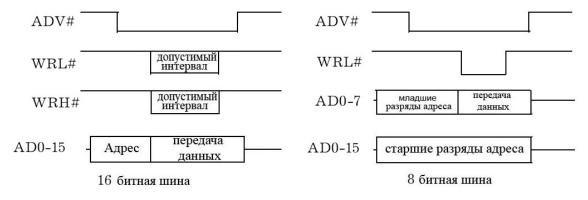

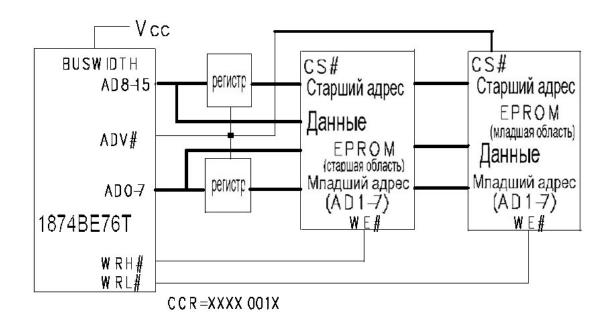

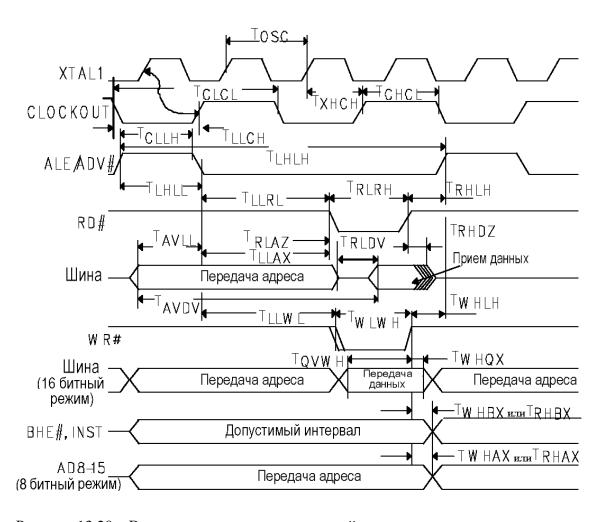

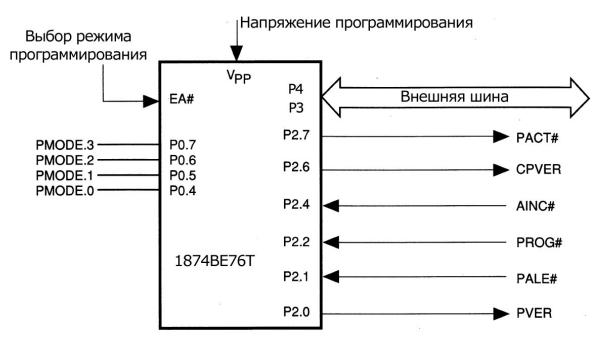

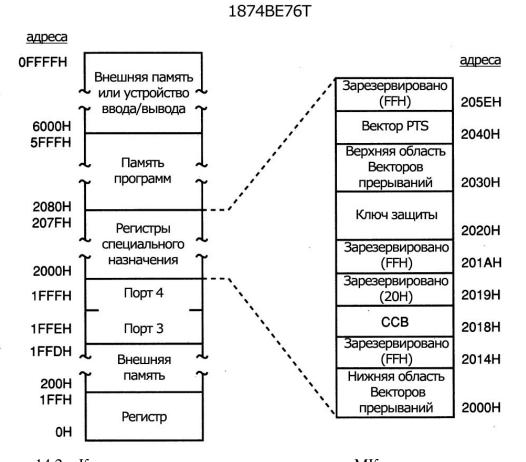

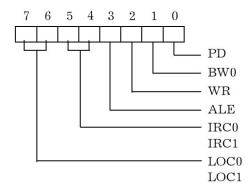

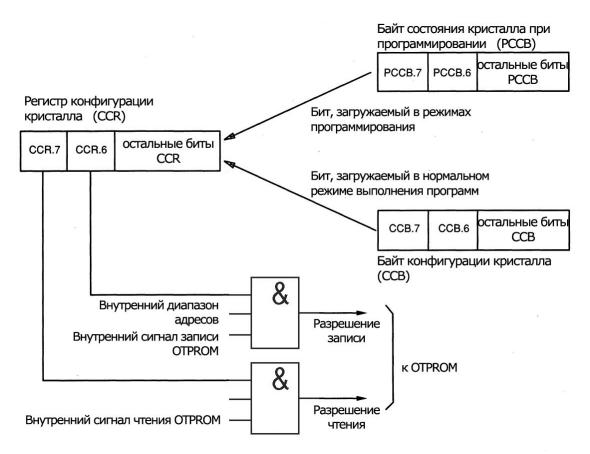

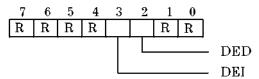

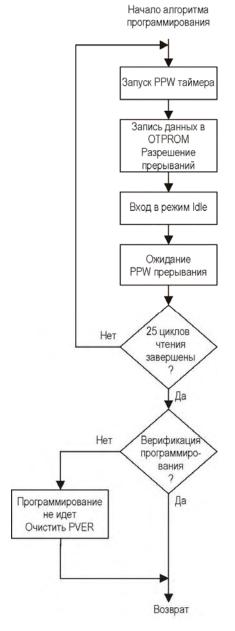

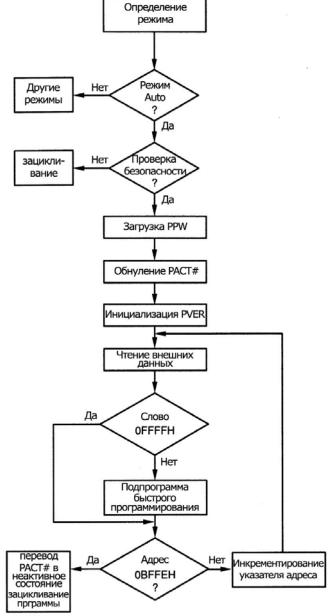

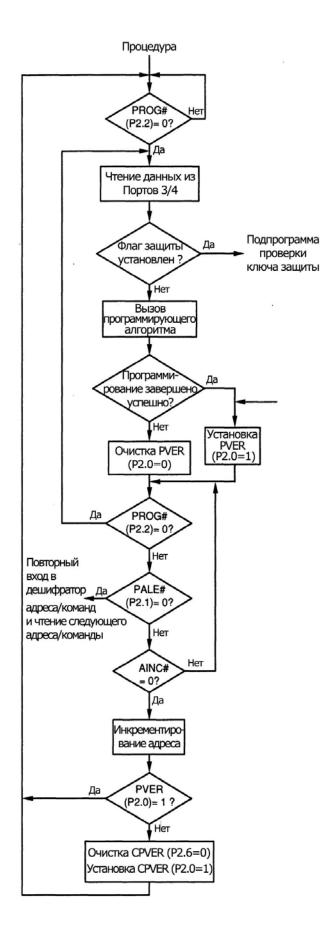

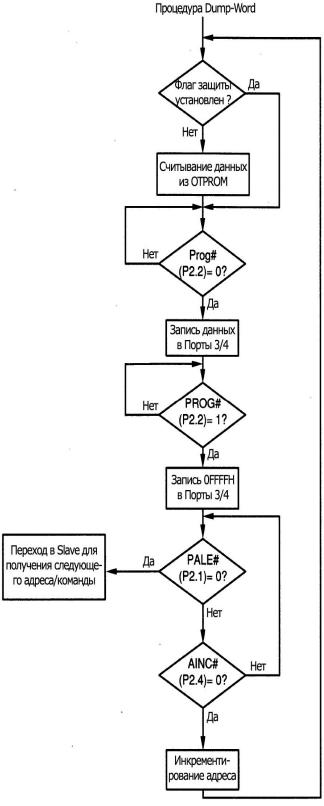

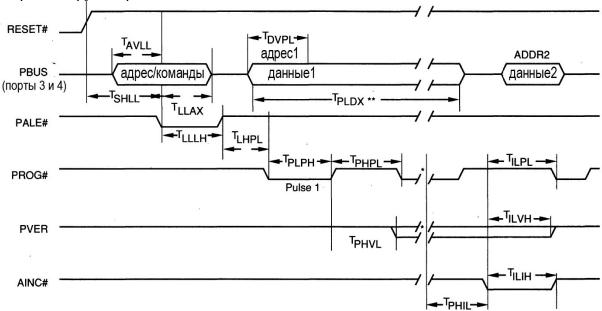

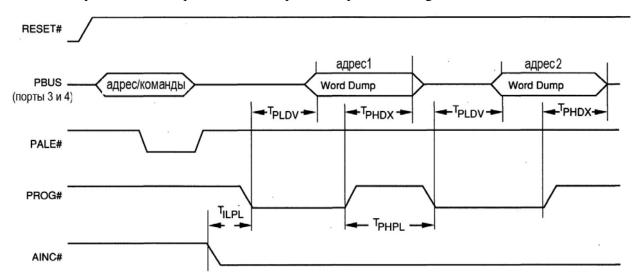

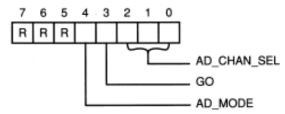

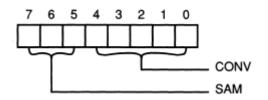

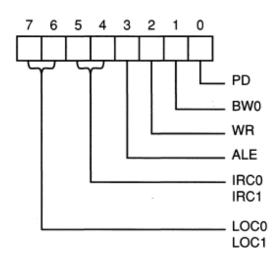

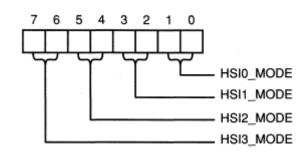

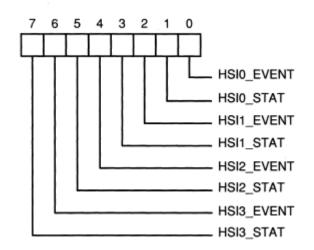

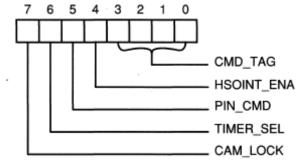

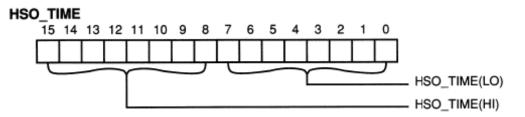

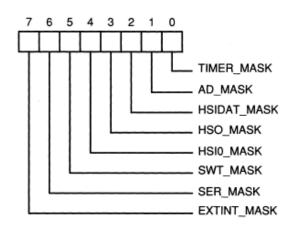

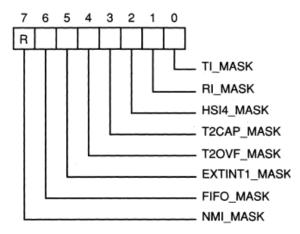

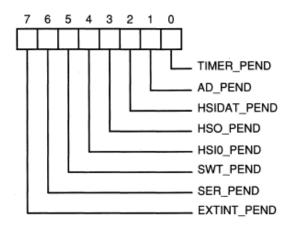

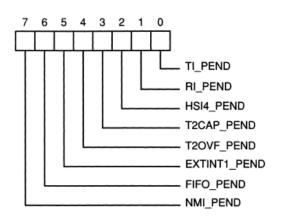

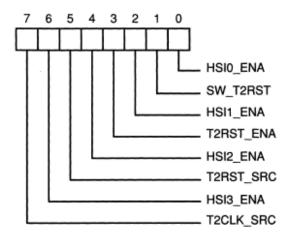

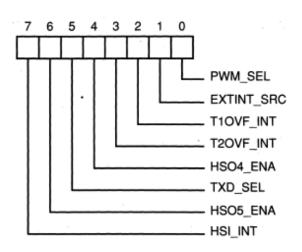

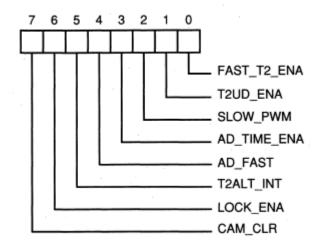

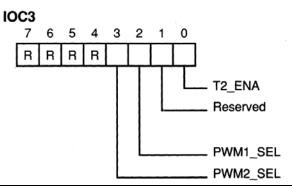

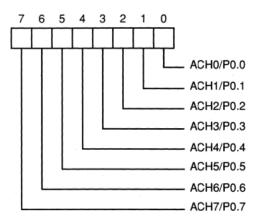

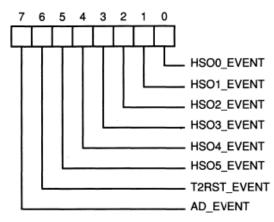

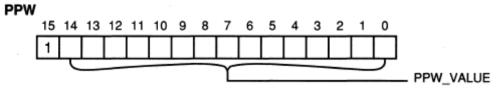

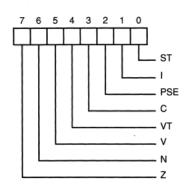

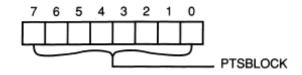

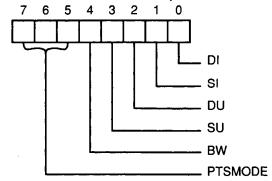

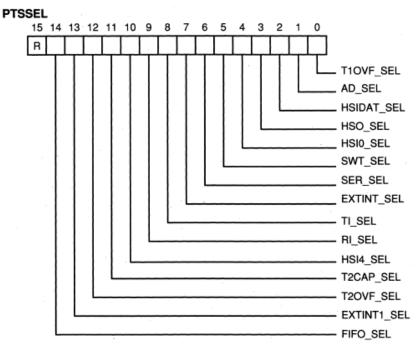

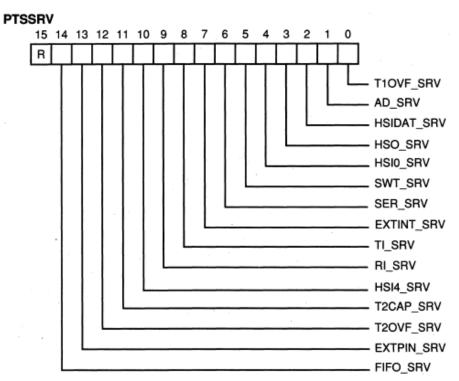

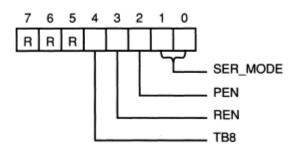

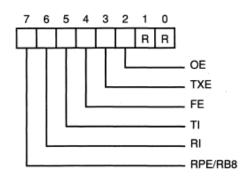

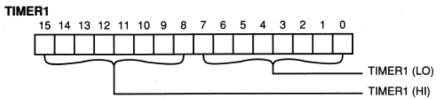

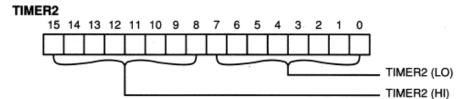

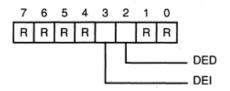

| 16 Входное напряжение высокого уровня |                                                                                                                                            | $U_{IHCI}$                 |                  |               |      |               |